1 pci type 0 configuration registers, Pci type 0 configuration registers -6 – Freescale Semiconductor MCF5480 User Manual

Page 490

MCF548x Reference Manual, Rev. 3

19-6

Freescale Semiconductor

19.3.1

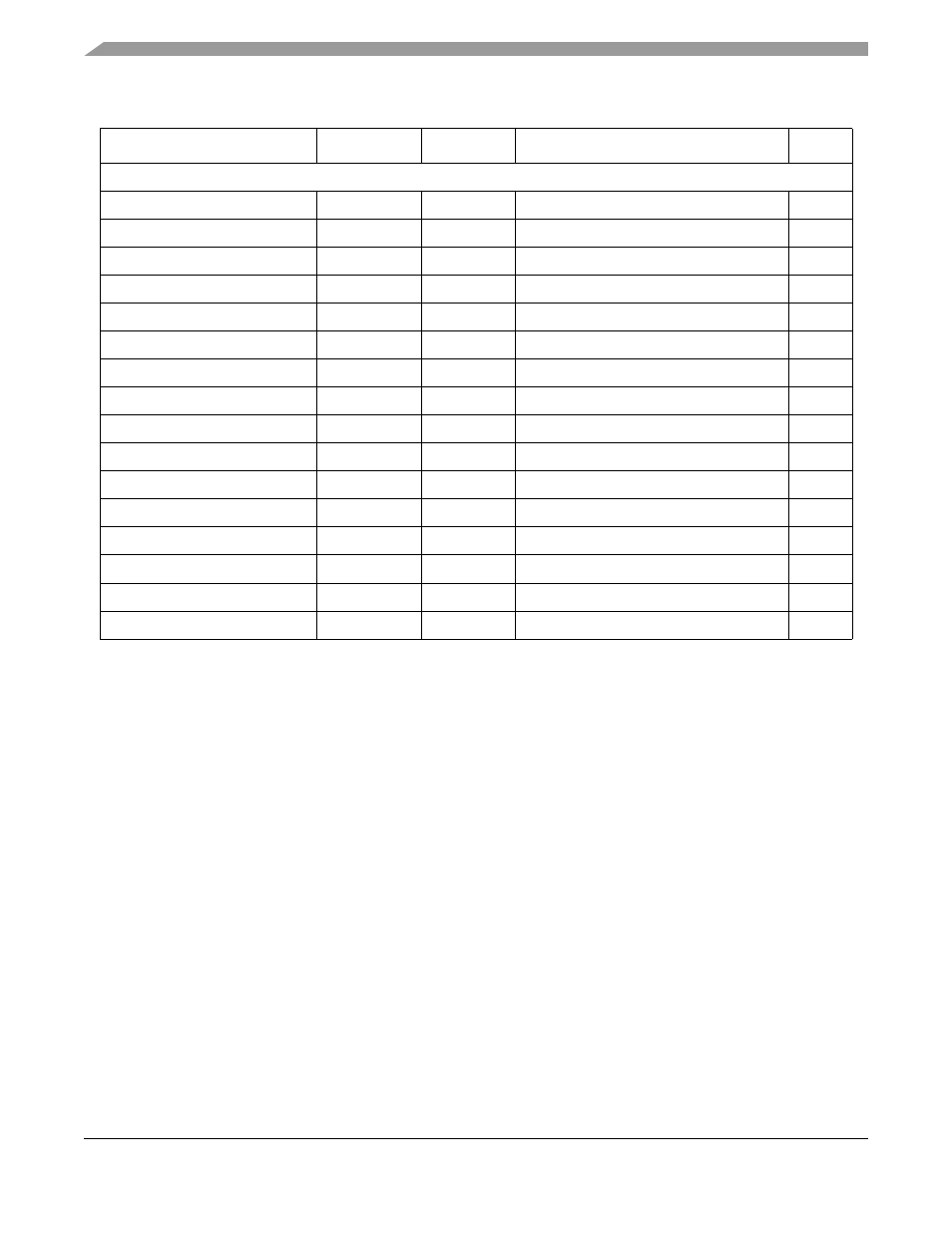

PCI Type 0 Configuration Registers

The PCI controller supplies a type 0 PCI configuration space header. These registers are accessible as an

offset from MBAR or through externally mastered PCI configuration cycles. PCI Dword Reserved space

(0x10–0x3F) can be accessed only from external PCI configuration accesses.

CommBus FIFO Receive Interface Registers

MBAR + 0x8480

PCIRPSR

32

Rx Packet Size Register

R/W

MBAR + 0x8484

PCIRSAR

32

Rx Start Address Register

R/W

MBAR + 0x8488

PCIRTCR

32

Rx Transaction Control Register

R/W

MBAR + 0x848C

PCIRER

32

Rx Enables Register

R/W

MBAR + 0x8490

PCIRNAR

32

Rx Next Address Register

R

MBAR + 0x8494

—

—

Reserved

—

MBAR + 0x8498

PCIRDCR

32

Rx Done Counts Register

R

MBAR + 0x849C

PCIRSR

32

Rx Status Register

R/WC

MBAR + 0x84A0–0x84BC

—

—

Reserved

—

MBAR + 0x84C0

PCIRFDR

32

Rx FIFO Data Register

R/W

MBAR + 0x84C4

PCIRFSR

32

Rx FIFO Status Register

R/WC

MBAR + 0x84C8

PCIRFCR

32

Rx FIFO Control Register

R/W

MBAR + 0x84CC

PCIRFAR

32

Rx FIFO Alarm Register

R/W

MBAR + 0x84D0

PCIRFRPR

32

Rx FIFO Read Pointer Register

R/W

MBAR + 0x84D4

PCIRFWPR

32

Rx FIFO Write Pointer Register

R/W

MBAR + 0x84D8–0x84FC

—

—

Reserved

—

1

The PCI controller has separate control registers for transmit and receive operations via the communication subsystem

DMA. See

Section 19.3.3, “Communication Subsystem Interface Registers

” for more information on these registers.

Table 19-2. PCI Memory Map (Continued)

Address

Name

Size

Description

Access