Freescale Semiconductor MCF5480 User Manual

Page 790

MCF548x Reference Manual, Rev. 3

26-28

Freescale Semiconductor

Reads from the PSCRFDRn register return received data from the Rx FIFO. In addition, this register

provides the possibility to fill the Rx FIFO for software development/debug purposes.

Writes to the PSCTFDRn register write data into the Tx FIFO. In addition, this register provides the

possibility to read data back from the Tx FIFO for software development/debug purposes.

Refer to

Section 26.3.3.6, “Receiver Buffer (PSCRBn) and Transmitter Buffer (PSCTBn)

”, for more

information about the data formats.

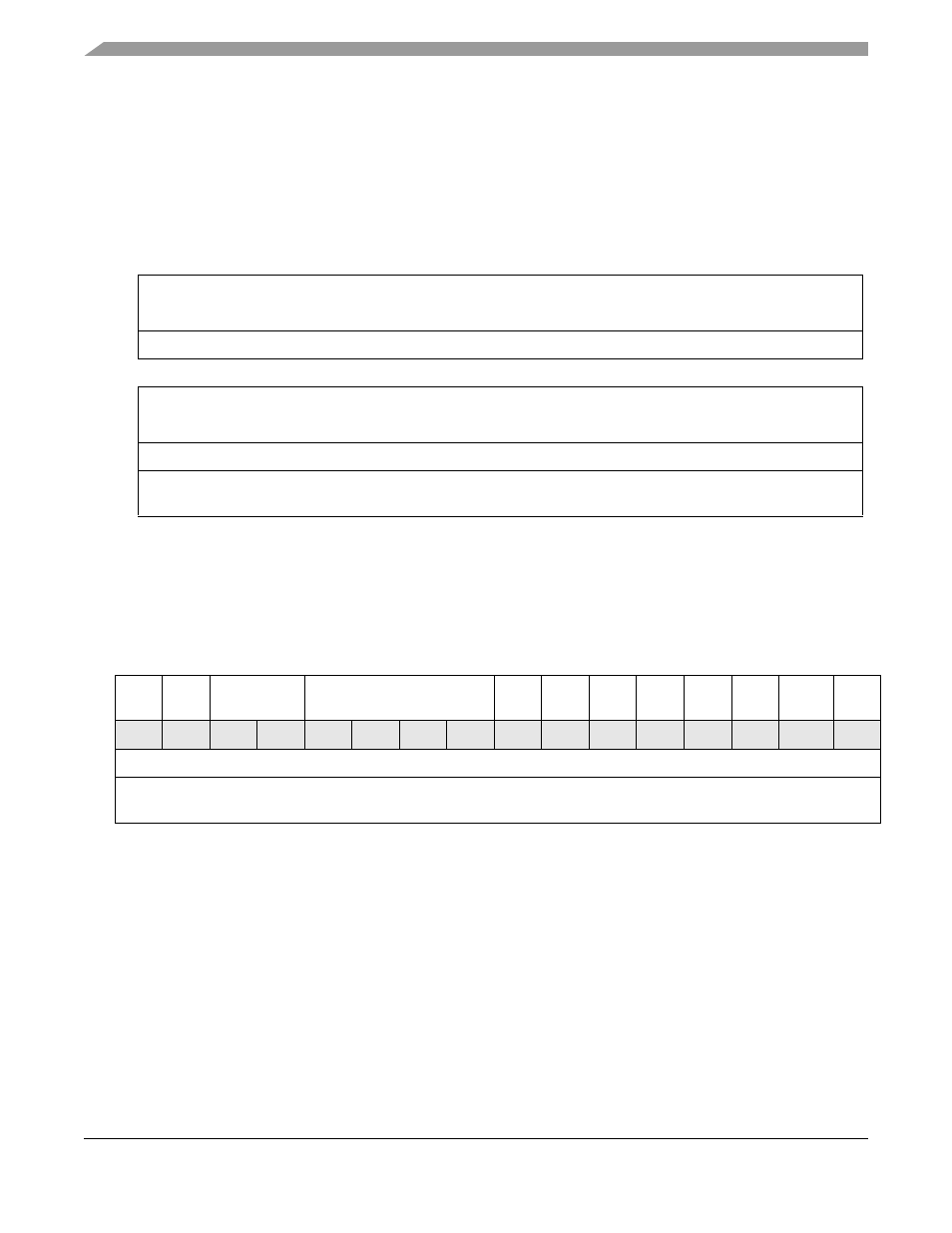

26.3.3.23 Rx and Tx FIFO Status Register (PSCRFSRn, PSCTFSRn)

The FIFO status registers contain bits which provide information about the status of the FIFO controller.

Some of the bits of this register are used to generate DMA requests. This register applies to all modes.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

DATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

DATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8660 (PSCRFDR0); 0x8760 (PSCRFDR1); 0x8860 (PSCRFDR2); 0x8960 (PSCRFDR3)

and MBAR + 0x8680 (PSCTFDR0); 0x8780 (PSCTFDR1); 0x8880 (PSCTFDR2); 0x8980 (PSCTFDR3)

Figure 26-19. RxFIFO (PSCRFDRn) and TxFIFO (PSCTFDRn) Data Register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

IP

TXW

TAG

FRM

FAE

RXW

UF

OF

FRM

RDY

FU

ALARM EMT

W

w1c

w1c

w1c

w1c

w1c

w1c

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Reg

Addr

MBAR + 0x8664 (PSCRFSR0); 0x8764 (PSCRFSR1); 0x8864 (PSCRFSR2); 0x8964 (PSCRFSR3)

and MBAR + 0x8684 (PSCTFSR0); 0x8784 (PSCTFSR1); 0x8884 (PSCTFSR2); 0x8984 (PSCTFSR3)

Figure 26-20. RxFIFO (PSCRFSR) and TxFIFO (PSCTFSR) Status Register