Table 7-8, The curren – Freescale Semiconductor MCF5480 User Manual

Page 249

Cache Operation Summary

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

7-29

the current state is valid.

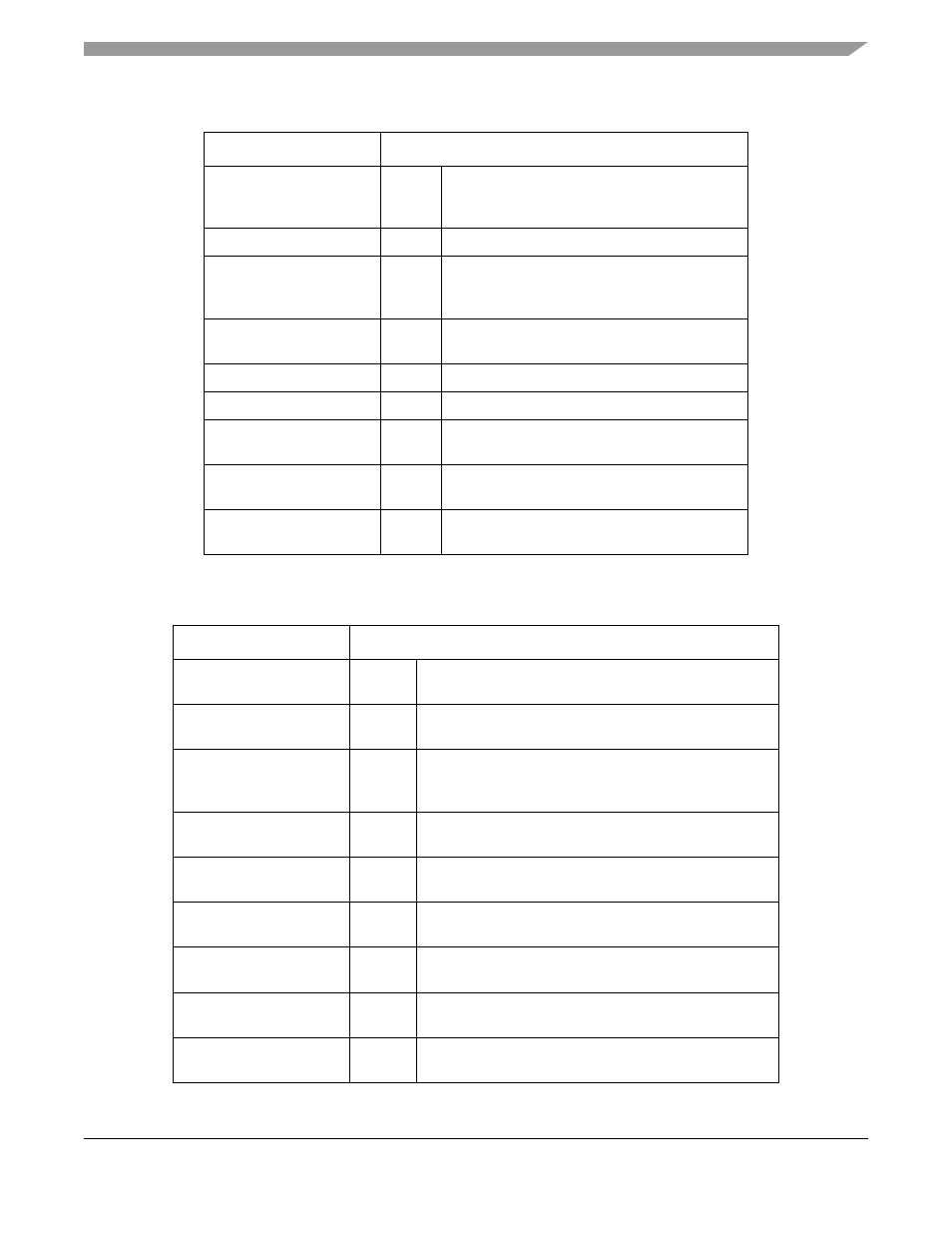

Table 7-8. Data Cache Line State Transitions (Current State Invalid)

Access

Response

Read miss

(C,W)I1 Read line from memory and update cache;

supply data to processor;

go to valid state.

Read hit

(C,W)I2 Not possible

Write miss (copyback)

CI3

Read line from memory and update cache;

write data to cache;

go to modified state.

Write miss (write-through)

WI3

Write data to memory;

stay in invalid state.

Write hit (copyback)

CI4

Not possible

Write hit (write-through)

WI4

Not possible

Cache invalidate

(C,W)I5 No action;

stay in invalid state.

Cache push

(C,W)I6 No action;

stay in invalid state.

Cache push

(C,W)I7 No action;

stay in invalid state.

Table 7-9. Data Cache Line State Transitions (Current State Valid)

Access

Response

Read miss

(C,W)V1

Read new line from memory and update cache;

supply data to processor; stay in valid state.

Read hit

(C,W)V2

Supply data to processor;

stay in valid state.

Write miss (copyback)

CV3

Read new line from memory and update cache;

write data to cache;

go to modified state.

Write miss (write-through)

WV3

Write data to memory;

stay in valid state.

Write hit (copyback)

CV4

Write data to cache;

go to modified state.

Write hit (write-through)

WV4

Write data to memory and to cache;

stay in valid state.

Cache invalidate

(C,W)V5

No action;

go to invalid state.

Cache push

(C,W)V6

No action;

go to invalid state.

Cache push

(C,W)V7

No action;

stay in valid state.