6 tx last word register (pcitlwr), 7 tx done counts register (pcitdcr) – Freescale Semiconductor MCF5480 User Manual

Page 512

MCF548x Reference Manual, Rev. 3

19-28

Freescale Semiconductor

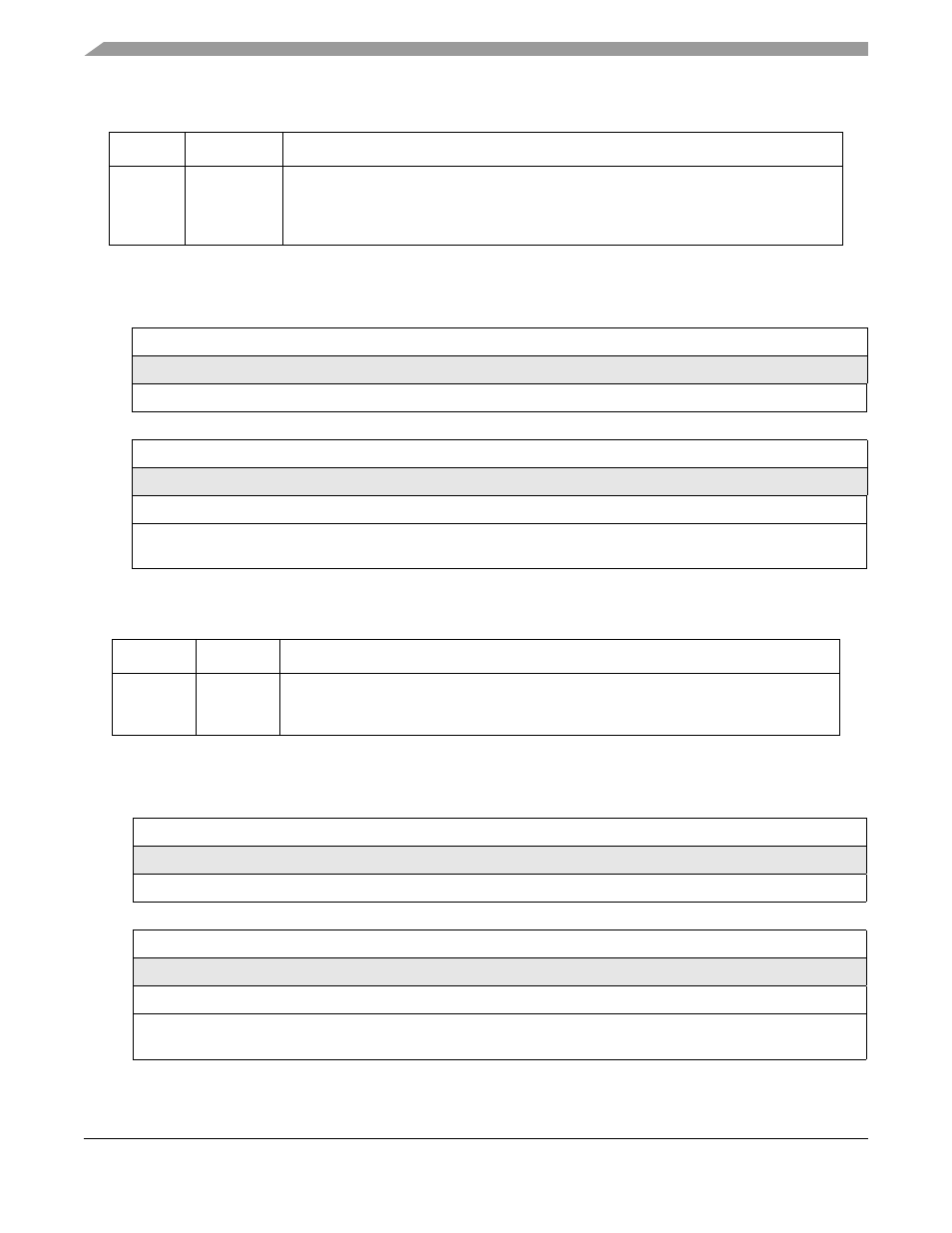

19.3.3.1.6

Tx Last Word Register (PCITLWR)

19.3.3.1.7

Tx Done Counts Register (PCITDCR)

Table 19-23. PCITNAR Field Descriptions

Bits

Name

Description

31–0

Next_Address This status register contains the next (unwritten) PCI address and is updated at the

successful completion of each PCI data beat. It represents a byte address and is updated

with the user-written Start_Add value whenever the Start_Add is reloaded. It is intended to

be accurate even in the case of abnormal terminations on the PCI bus.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Last_Word

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Last_Word

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8414

Figure 19-25. Tx Last Word Register (PCITLWR)

Table 19-24. PCITLWR Field Descriptions

Bits

Name

Description

31–0

Last_Word

This status register indicates the last 32-bit data fetched from the FIFO and is designed for

the case in which an abnormal PCI termination has corrupted the integrity of the FIFO data

(for that word).

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Bytes_Done

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Packets_Done

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8418

Figure 19-26. Tx Done Counts Register (PCITDCR)