11 rx fifo alarm register (pcirfar) – Freescale Semiconductor MCF5480 User Manual

Page 530

MCF548x Reference Manual, Rev. 3

19-46

Freescale Semiconductor

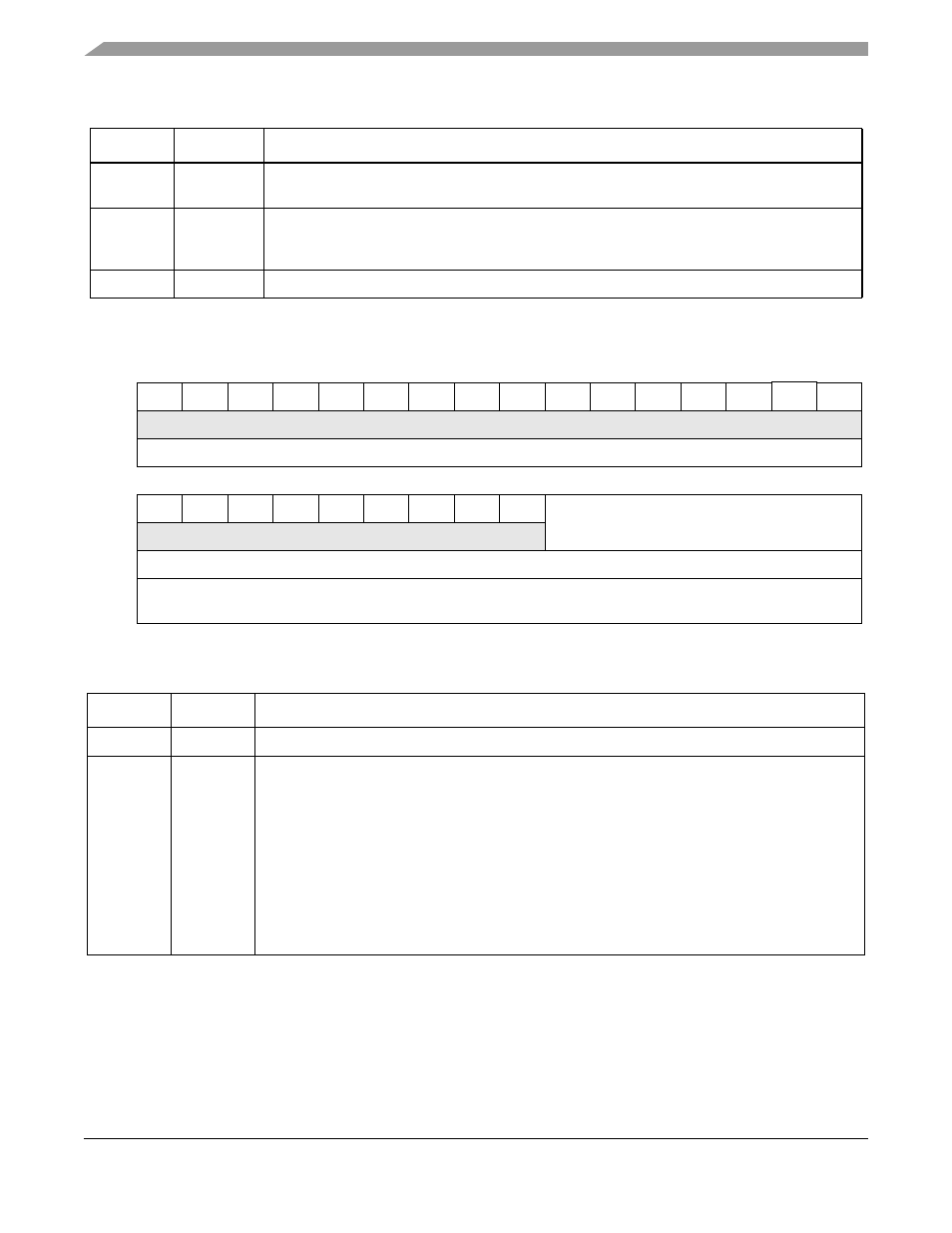

19.3.3.2.11 Rx FIFO Alarm Register (PCIRFAR)

19

OF_MASK

Overflow mask. When this bit is set, the FIFO controller masks the Status Register’s OF bit from

generating an error.

18

TXW_MASK Transmit wait condition mask. When this bit is set, the FIFO controller masks the Status

Register’s TXW bit from generating an error. (To help with backward compatibility, this bit is

asserted at reset.)

17–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

Alarm

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x84CC

Figure 19-44. Rx FIFO Alarm Register (PCIRFAR)

Table 19-43. PCIRFAR Field Descriptions

Bits

Name

Description

31–7

—

Reserved, should be cleared.

6–0

Alarm

Bits 6-0 are programmable to control a 128-byte FIFO. User writes these bits to set the low level

watermark, which is the point at which the FIFO asserts its request for data emptying to the

Multi-Channel DMA controller. This value is in free bytes. For example, with Alarm = 32 (0x20), the

alarm condition will occur when the FIFO has 32 or less free bytes in it. The alarm, once asserted,

will not negate until the high level mark is reached, when there is GR[2:0] or less bytes remaining

in the FIFO.

Note: The Alarm setting should be programmed to a value greater than or equal to Max_Beats *

4 or else data transfer may stall. The Rx controller waits for enough space to be available in the

FIFO for it to write a burst of Max_Beats * 4 bytes before it will request data from the PCI bus. For

a Max_Beats value of 0(8 beats), Alarm should be programmed to 32 or greater.

Table 19-42. PCIRFCR Field Descriptions (Continued)

Bits

Name

Description