1 8-bit podr_x registers, 2 7-bit podr_x register – Freescale Semiconductor MCF5480 User Manual

Page 381

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

15-9

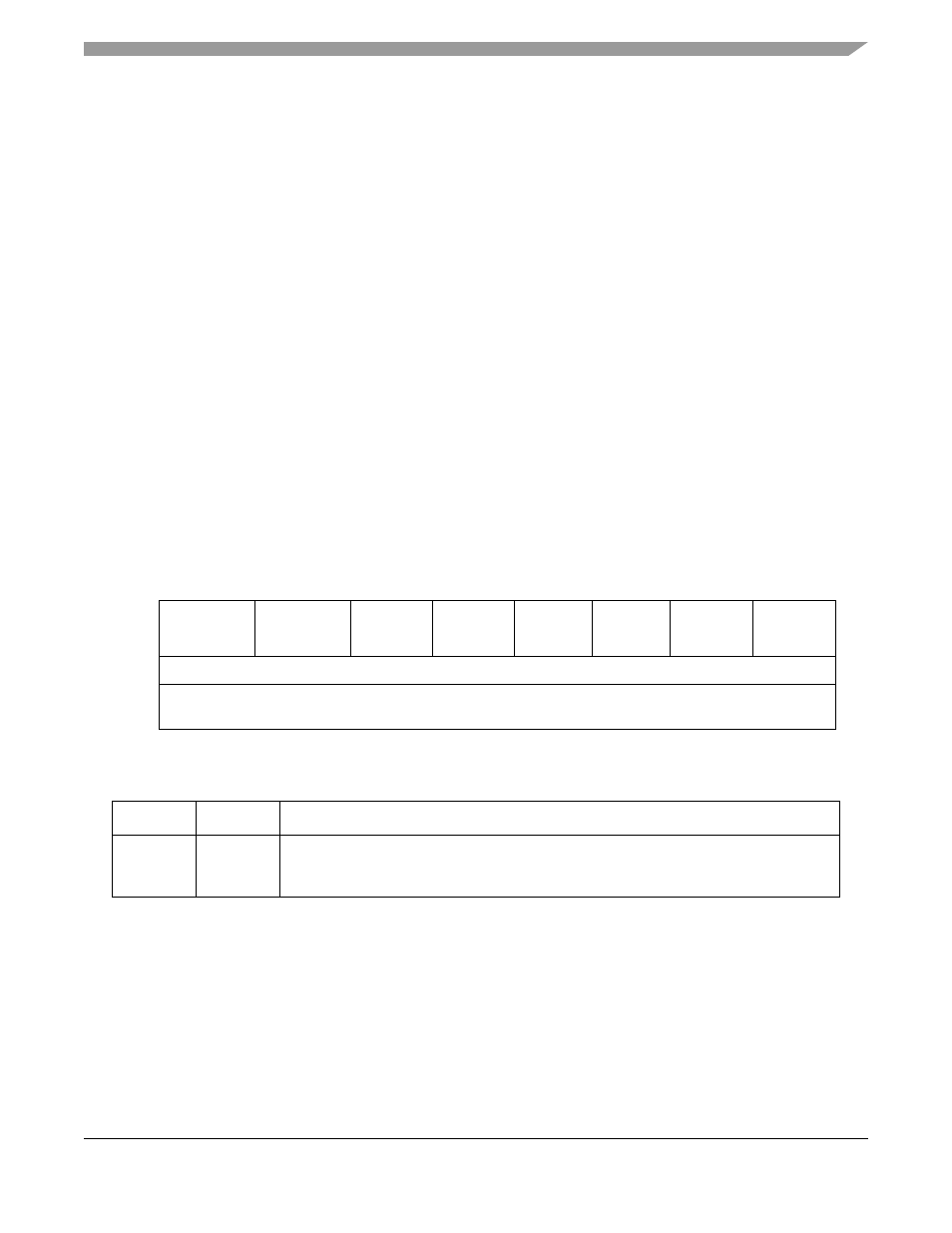

Most PODR_x registers have full 8-bit implementations, as shown in

. The remaining PODR_x

registers use fewer than eight bits. These registers are shown in

, and

The PODR_x registers are read/write. At reset, all implemented bits in the PODR_x registers are set.

Unimplemented bits always remain cleared.

Reading a PODR_x register returns the current values in the register, not the port x pin values.

To set bits in a PODR_x register, write 1s to the PODR_x bits, or write 1s to the corresponding bits in the

PORTP_x/SET_x register. To clear bits in a PODR_x register, write 0s to the PODR_x bits, or write 0s to

the corresponding bits in the PCLRR_x register.

15.3.2.1.1

8-Bit PODR_x Registers

The 8-bit PODR_x registers include the following:

•

PODR_FBCTL

•

PODR_FEC0H

•

PODR_FEC0L

•

PODR_FEC1H

•

PODR_FEC1L

•

PODR_PSC3PSC2

•

PODR_PSC1PSC0

displays the 8-bit PODR_x registers.

15.3.2.1.2

7-Bit PODR_x Register

The 7-bit PODR_DSPI register is the output data register for the PDSPIn port.

7-bit PODR_x register.

7

6

5

4

3

2

1

0

R

PODRx7

PODRx6

PODRx5

PODRx4

PODRx3

PODRx2

PODRx1

PODRx0

W

Reset

1

1

1

1

1

1

1

1

Reg

Addr

MBAR + 0xA00 (PODR_FBCTL), 0xA04 (PODR_FEC0H), 0xA05 (PODR_FEC0L), 0xA06 (PODR_FEC1H),

0xA07 (PODR_FEC1L), 0xA0C (PODR_PSC3PSC2), 0xA0D (PODR_PSC1PSC0)

Figure 15-2. 8-Bit Port Output Data Registers (PODR_x)

Table 15-4. 8-Bit PODR_x Field Descriptions

Bits

Name Description

7–0

PODRxn

PODRx Output Data Bits

0 Drive 0 when PORT x pin is general purpose output

1 Drive 1 when PORT x pin is general purpose output