The fpcr, Figure 6-9 – Freescale Semiconductor MCF5480 User Manual

Page 198

MCF548x Reference Manual, Rev. 3

6-8

Freescale Semiconductor

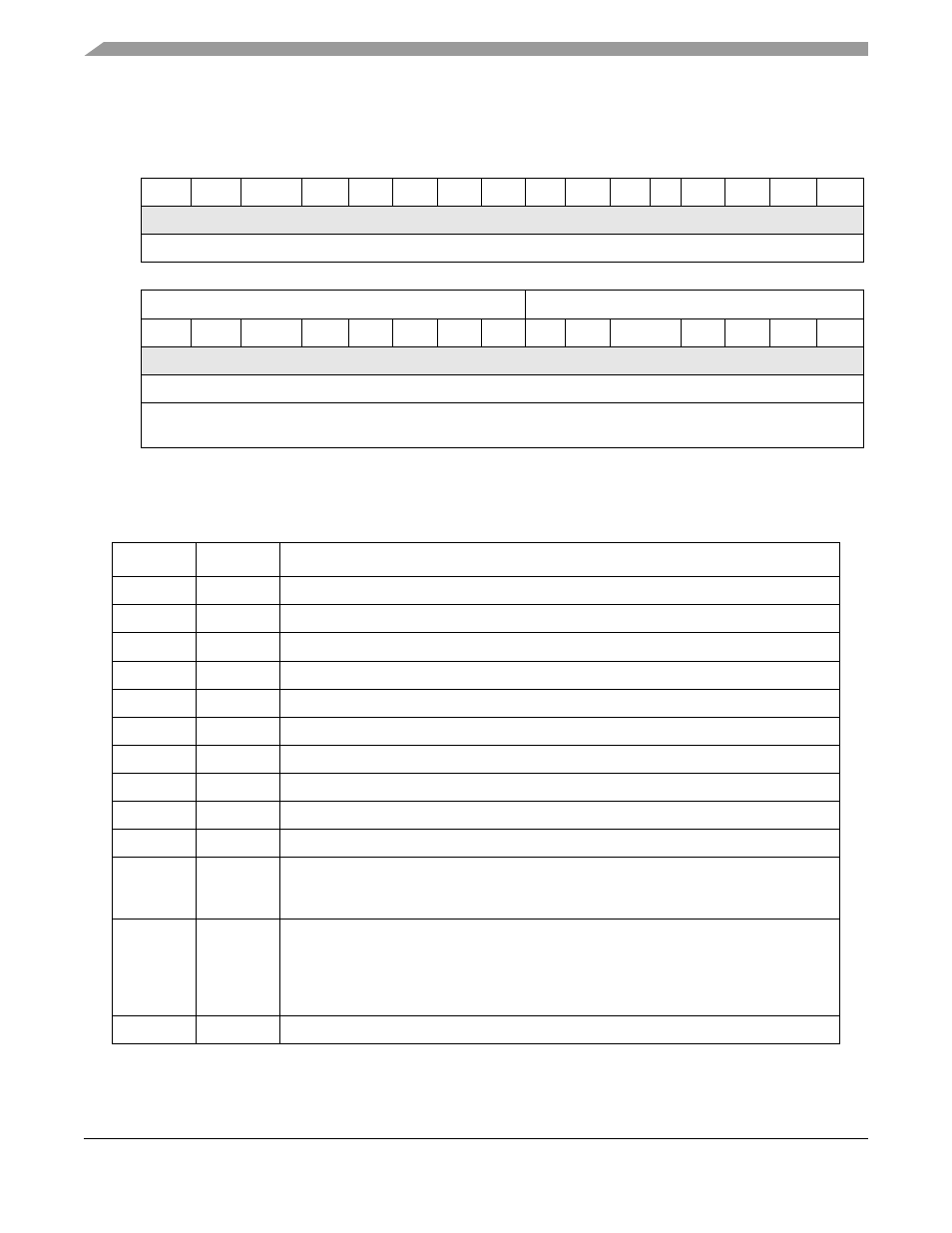

The user can read or write to FPCR using FMOVE or FRESTORE. A processor reset or a restore operation

of the null state clears the FPCR. When this register is cleared, the FPU never generates exceptions.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Exception Enable Byte (EE)

Mode Control Byte (MC)

R BSUN

INAN

OPERR OVFL UNFL

DZ

INEX

IDE

0

PREC

RND

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0x824

Figure 6-9. Floating-Point Control Register (FPCR)

Table 6-4. FPCR Field Descriptions

Bits

Field

Description

31–16

—

Reserved, should be cleared.

15

BSUN

Branch set on unordered

14

INAN

Input not-a-number

13

OPERR

Operand error

12

OVFL

Overflow

11

UNFL

Underflow

10

DZ

Divide by zero

9

INEX

Inexact operation

8

IDE

Input denormalized

7

—

Reserved, should be cleared.

6

PREC

Rounding precision

0 Double (D)

1 Single (S)

5–4

RND

Rounding mode

00 To nearest (RN)

01 To zero (RZ)

10 To minus infinity (RM)

11 To plus infinity (RP)

3–0

—

Reserved, should be cleared.