Freescale Semiconductor MCF5480 User Manual

Page 782

MCF548x Reference Manual, Rev. 3

26-20

Freescale Semiconductor

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Mode

R

IPC

0

0

0

0

0

RXRDY_FU TXRDY

DEOF ERR

0

0

0

0

0

0

MIR /

FIR

W

R

IPC

0

0

0

0

0

RXRDY_FU TXRDY

0

ERR

0

0

0

0

0

0

Modem

W

R

IPC

0

0

0

0

DB RXRDY_FU TXRDY

0

ERR

0

0

0

0

0

0

UART

W

R

IPC

0

0

0

0

DB RXRDY_FU TXRDY

DEOF ERR

0

0

0

0

0

0

SIR

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8614 (PSC0); 0x8714 (PSC1); 0x8814 (PSC2); 0x8914 (PSC3)

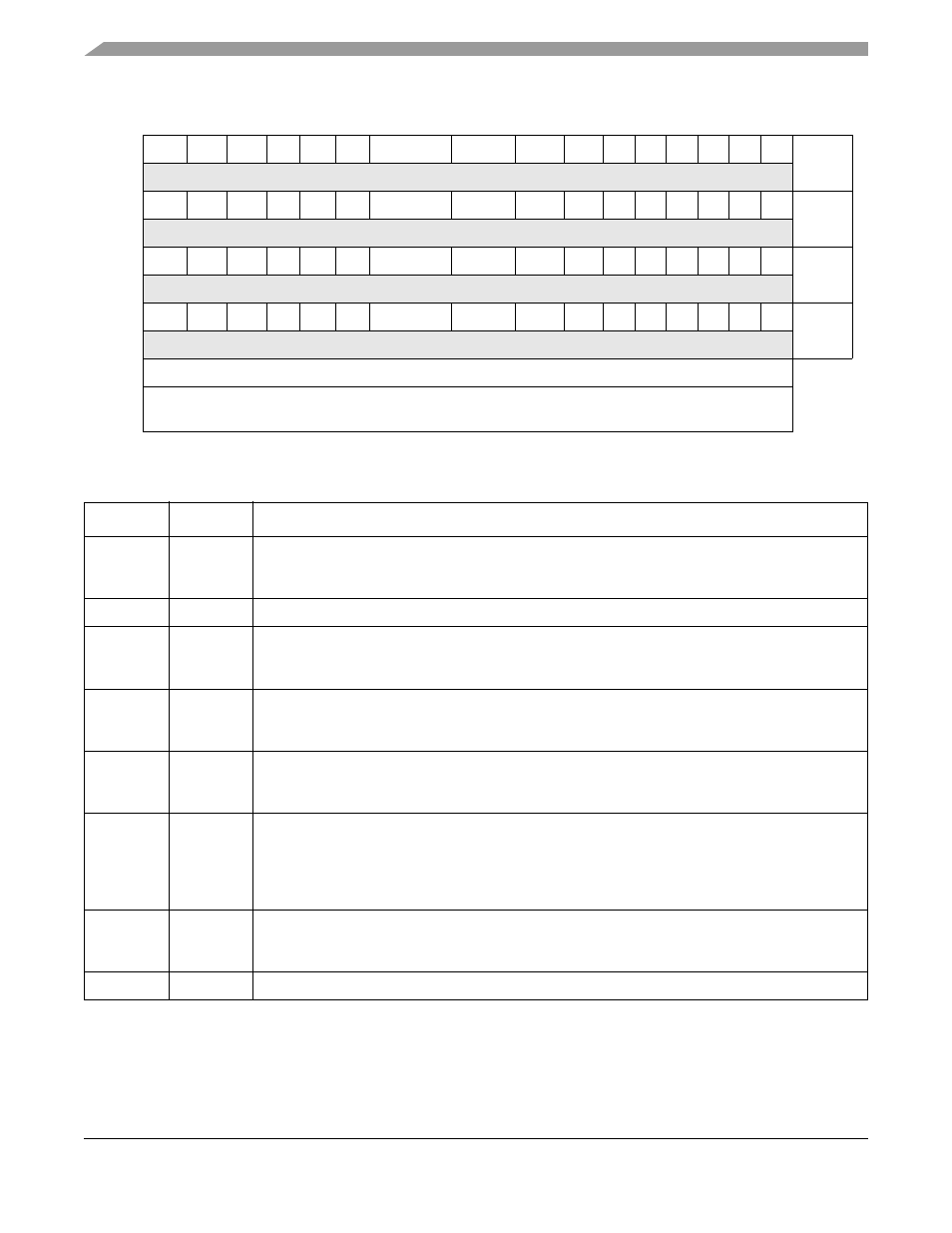

Figure 26-15. Interrupt Mask Register (PSCIMRn)

Table 26-14. PSCIMRn Field Descriptions

Bits

Name

Description

15

IPC

Input port change interrupt

0 IPC has no effect on the interrupt.

1 Enable the interrupt for IPC in the PSCISR.

14–11

—

Reserved, should be cleared.

10

DB

In UART / SIR , this is a delta break interrupt. In other modes, this is reserved.

0 DB has no effect on the interrupt.

1 Enable the interrupt for DB in the PSCISR register.

9

RXRDY_FU RxFIFO interrupt, see PSCISR[RXRDY_FU) in

0 PSCISR[RXRDY] or PSCISR[FU] has no effect on the interrupt.

1 Enable the interrupt for RXRDY or FU in the PSCISR.

8

TXRDY

TXRDY interrupt

0 TXRDY has no effect on the interrupt.

1 Enable the interrupt for TXRDY in the PSCISR.

7

DEOF

For modem and UART modes this bit is reserved.

For SIR MIR mode, this bit signifies Detect End of Frame or RxFIFO contains EOF

0 FEOF has no effect on the interrupt

1 Enable the interrupt for DEOF in the PSCISR

6

ERR

OR of all errors status including FIFO errors.

0 No error was detected.

1 At least one error occurred

5–0

—

Reserved, should be cleared.