Freescale Semiconductor MCF5480 User Manual

Page 365

Memory Map/Register Descriptions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

13-13

13.2.1.7

Software and Level n IACK Registers (SWIACKR, L1IACK–L7IACK)

The eight IACK registers can be explicitly addressed via the CPU, or implicitly addressed via a

processor-generated interrupt acknowledge cycle during exception processing. In either case, the interrupt

controller’s actions are very similar.

First, consider an IACK cycle to a specific level: that is, a level-n IACK. When this type of IACK arrives

in the interrupt controller, the controller examines all the currently-active level-n interrupt requests,

36

CommTim

TC

Combined interrupts from comm

timers

Write ‘1’ to CTCRn[I]

37

SEC

—

SEC interrupt

Service interrupt and write ‘1’ to SICR

38

FEC1

—

FEC1 interrupt

Write appropriate interrupt condition bit = 1

39

FEC0

—

FEC0 interrupt

Write appropriate interrupt condition bit = 1

40

I2C

—

I2C interrupt

Write IIF = 0

41

PCIARB

—

PCI arbiter interrupt

Write ‘1’ to PASR[EXTMBK] or PASR[ITLMBK]

42

CBPCI

—

Comm bus PCI interrupt

Clear FIFO alarm condition

43

XLBPCI

—

XLB PCI interrupt

Write ‘1’ to appropriate PCIISR bit(s)

44–46

Not used

47

XLBARB

—

XLBARB to CPU interrupt

Write ‘1’ to appropriate ARB_SR bit(s)

48

DMA

—

Multichannel DMA interrupt

Write ‘1’ to DIPR[TASKn]

49

CAN0

ERROR

FlexCAN error interrupt

Read error bits in ESR or write ERR_INT = 0

50

BUSOFF

FlexCAN bus off interrupt

Write BOFF_INT = 0

51

MBOR

Message buffer ORed interrupt

Write BUFnI = 1 after reading BUFnI = 1

52

Not used

53

Slice

Timer

SLT1

Slice timer 1 interrupt

Write ST = 1

54

SLT0

Slice timer 0 interrupt

Write ST = 1

55

CAN1

ERROR

FlexCAN error interrupt

Read error bits in ESR or write ERR_INT = 0

56

BUSOFF

FlexCAN bus off interrupt

Write BOFF_INT = 0

57

MBOR

Message buffer ORed interrupt

Write BUFnI = 1 after reading BUFnI = 1

58

Not used

59

GPTs

GPT3

GPT3 interrupt

Write ‘1’ to appropriate GSR bit

60

GPT2

GPT2 interrupt

Write ‘1’ to appropriate GSR bit

61

GPT1

GPT1 interrupt

Write ‘1’ to appropriate GSR bit

62

GPT0

GPT0 interrupt

Write ‘1’ to appropriate GSR bit

63

Not used

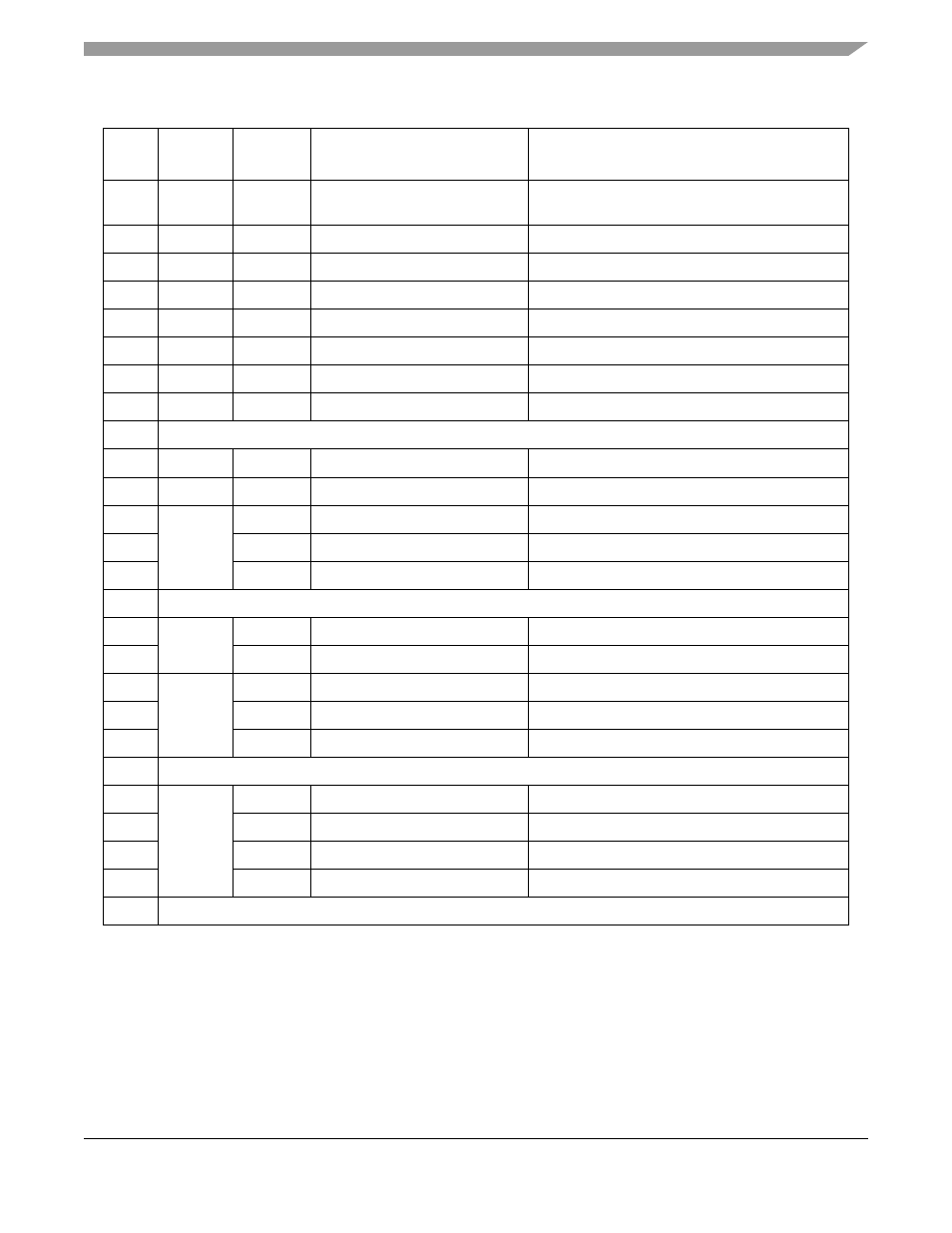

Table 13-12. Interrupt Source Assignments (Continued)

Sourc

e

Module

Flag

Source Description

Flag Clearing Mechanism