1 resulting set of possible trigger combinations, Resulting set of possible trigger combinations -27 – Freescale Semiconductor MCF5480 User Manual

Page 277

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

8-27

8.4.11.1

Resulting Set of Possible Trigger Combinations

The resulting set of possible breakpoint trigger combinations consist of the following options where ||

denotes logical OR, && denotes logical AND, and {} denotes an optional additional trigger term:

One-level triggers of the form:

if

(PC_breakpoint)

if

(PC_breakpoint|| Address_breakpoint{&& Data_breakpoint})

if

(PC_breakpoint|| Address_breakpoint{&& Data_breakpoint}

||

Address1_breakpoint{&& Data1_breakpoint})

if

(Address_breakpoint

{&& Data_breakpoint})

if

((Address_breakpoint

{&& Data_breakpoint})

||

(Address1_breakpoint{&& Data1_breakpoint}))

if

(Address1_breakpoint

{&& Data1_breakpoint})

Two-level triggers of the form:

if

(PC_breakpoint)

then if

(Address_breakpoint{&& Data_breakpoint})

if

(PC_breakpoint)

then if

(Address_breakpoint{&& Data_breakpoint}

||

Address1_breakpoint{&& Data1_breakpoint})

if

(PC_breakpoint)

then if

(Address1_breakpoint{&& Data1_breakpoint})

if

(Address_breakpoint

{&& Data_breakpoint})

then if

(Address1_breakpoint{&& Data1_breakpoint})

if

(Address1_breakpoint

{&& Data1_breakpoint})

then if

(Address_breakpoint{&& Data_breakpoint})

if

(Address_breakpoint

{&& Data_breakpoint})

then if

(PC_breakpoint)

if

(Address1_breakpoint

{&& Data1_breakpoint})

then if

(PC_breakpoint)

if

(Address_breakpoint

{&& Data_breakpoint})

3

EAR1

Address enable bit: Enable address breakpoint range. The breakpoint is based on the inclusive

range defined by ABLR1 and ABHR1. Trigger if address Š ABHR or if address ð ABLR.

2

EAL1

Address enable bit: Enable address breakpoint low. The breakpoint is based on the address in the

ABLR1. Trigger address = ABLR

1–0

—

Reserved, should be cleared.

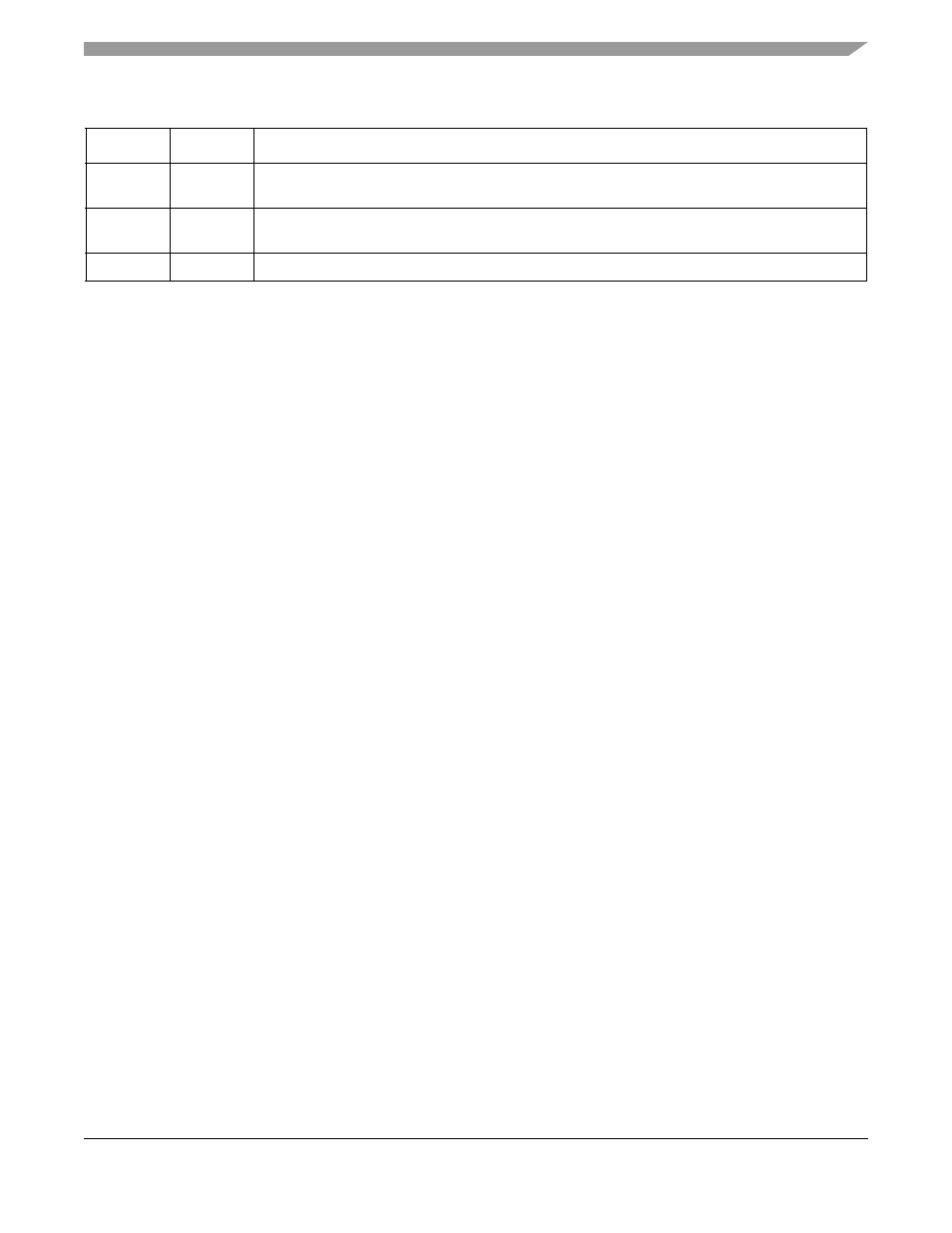

Table 8-21. XTDR Field Descriptions (Continued)

Bits

Name

Description