3 dma registers, 1 dma register map, Dma registers -5 – Freescale Semiconductor MCF5480 User Manual

Page 725: Dma register map -5

Memory Map/Register Definitions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

24-5

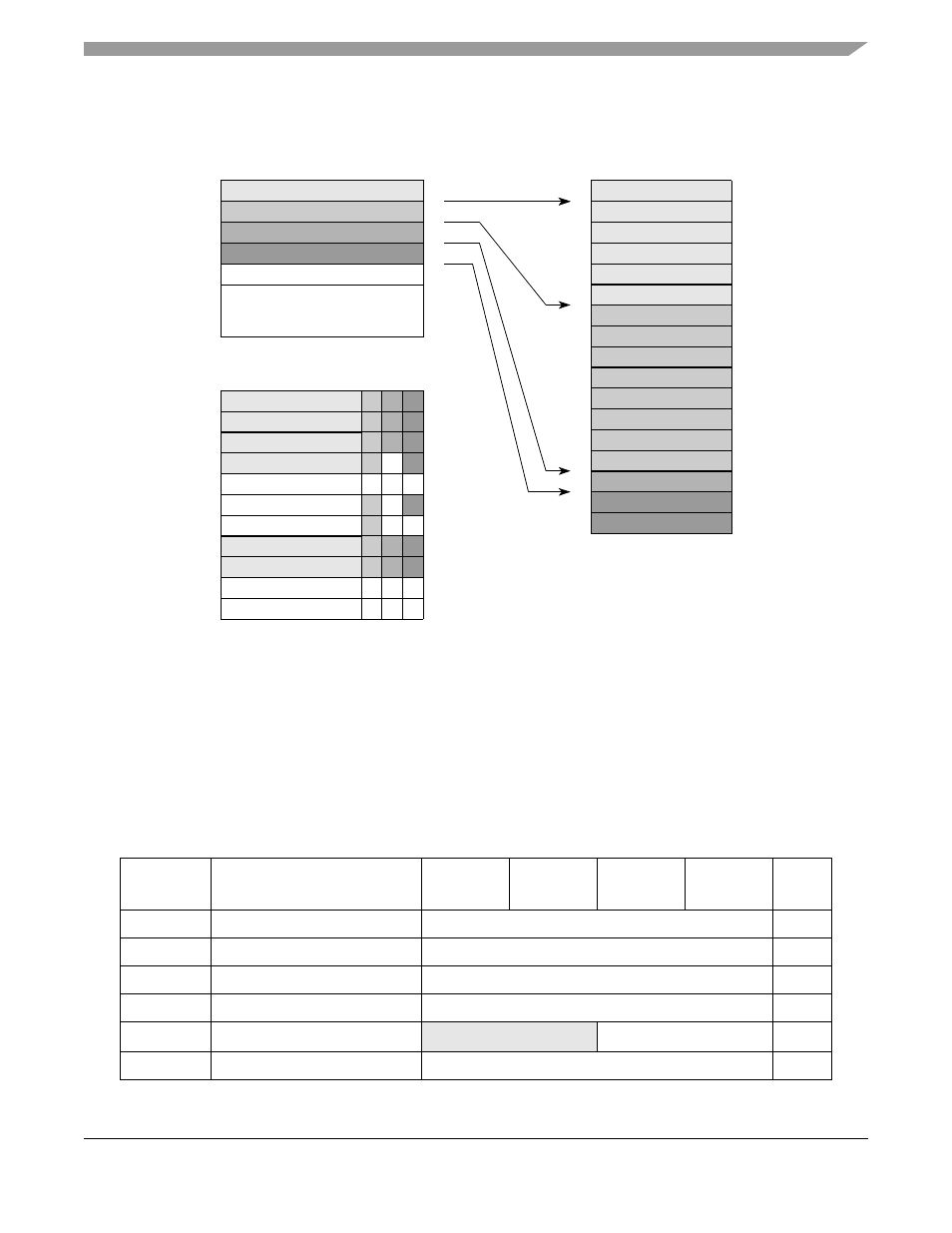

Figure 24-2. DMA Programmer-Maintained Memory Model

24.3.3

DMA Registers

24.3.3.1

DMA Register Map

shows the memory map of the DMA module.

Table 24-1. DMA Memory Map

Address

(MBAR +)

Name

Byte0

Byte1

Byte2

Byte3

Access

0x8000

Task Base Address Register

TaskBAR

R/W

0x8004

Current Pointer

CP

R

0x8008

End Pointer

EP

R

0x800C

Variable Pointer

VP

R

0x8010

PTD Control Register

PTD

R/W

0x8014

DMA Interrupt Pending Register

DIPR

R/W

Start, End,

Variable Table Pointer,

Control

Task 0 Pointers, Control

LCD0

0

DRD0

1

LCD1

2

LCD2

3

DRD2

4

DRD1

5

LCD3

6

LCD4

7

DRD4

8

DRD3

9

LCD5

10

LCD6

11

DRD6

12

DRD5

13

LCD7

n–1

DRD7

n

Task 1 Pointers, Control

Task 2 Pointers, Control

Task 3 Pointers, Control

Initial Value0

0

Initial Value1

1

Initial Value2

2

Initial Value3

3

22

23

Increment0

24

Increment1

25

31

Task 0

Task 1

Task 2

Task 3

Task 15

•

•

•

••

•

••

•

Variable Table

Pointed to by Task Table

Task Table

Pointed to by TaskBAR

Task Descriptor Table

Programmer-Maintained,

Located in Memory

Shadings indicate different tasks.

Four tasks shown.