Freescale Semiconductor MCF5480 User Manual

Page 216

MCF548x Reference Manual, Rev. 3

6-26

Freescale Semiconductor

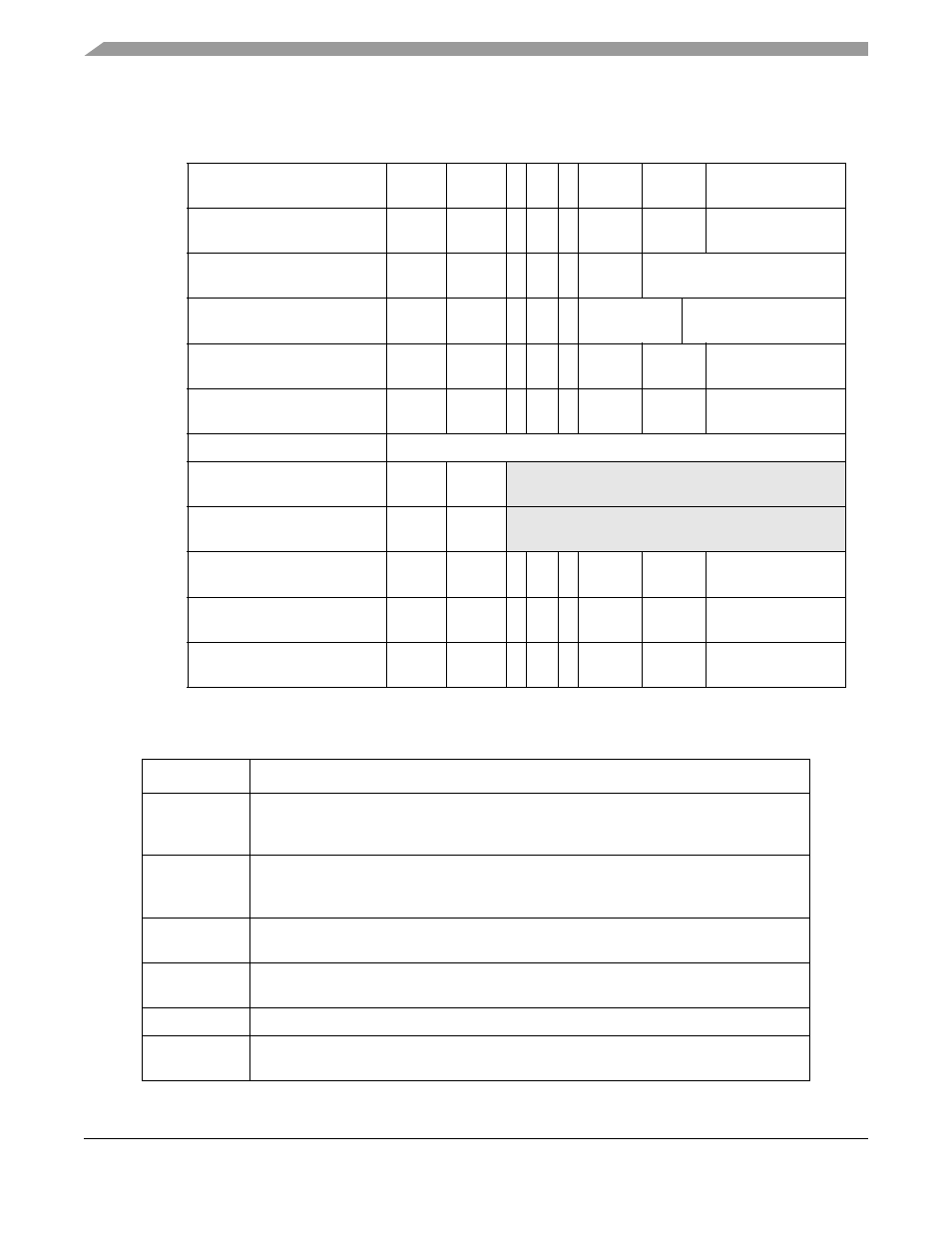

defines the terminology used in

FMOVE

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0

1

1

dest fmt

src reg

0 0 0 0 0 0 0

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

1

0

d

r

reg sel

0 0

0

0 0 0 0 0 0 0

FMOVEM

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

1

1

d

r

1 0

0

0 0

register list

FMUL

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FNEG

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FNOP

1 1 1 1 0 0 1 0 1 0 0 0 0 0 0 0 0

0

0 0 0

0

0 0

0

0 0 0 0 0 0 0

FRESTOR

E

1 1 1 1 0 0 1 1 0 1

ea

mode

ea reg

FSAVE

1 1 1 1 0 0 1 1 0 0

ea

mode

ea reg

FSQRT

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FSUB

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FTST

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg 0 1 1 1 0 1 0

Table 6-24. Instruction Format Terminology

Term

Definition

Instructions

Instructions appear in memory as sequential, 16-bit values, and are read in the above table

left to right. An instruction can have from 1 to 3 16-bit words. A shaded block indicates this

word is never used and is not present.

EA MODE

EA REG

Defines the effective address for an operand located external to the FPU. For most FPU

instructions, this field defines the location of an external source operand; for FP store

operations, it specifies the destination location.

R/M

If R/M = 0, an FPU data register is one source operand, otherwise the source operand is

specified by the EA {MODE, REG} fields.

SRC SPEC

Defines the format (byte, word, longword, single-, or double-precision) of an external

operand.

DEST REG

Specifies the destination FPU data register.

COND

PREDICATE

Defines the condition to be evaluated (EQ, NE, and so on) during the execution of the FPU

conditional branch instruction.

Table 6-23. Floating-Point Instruction Formats (Continued)

Mnemonic

Instruction Code