5 supervisor programming model, Supervisor programming model -11 – Freescale Semiconductor MCF5480 User Manual

Page 115

Programming Model

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

3-11

•

Eight 64-bit floating-point data registers (FP0–FP7)

•

One 32-bit floating-point control register (FPCR)

•

One 32-bit floating-point status register (FPSR)

•

One 32-bit floating-point instruction address register (FPIAR)

shows the FPU programming model.

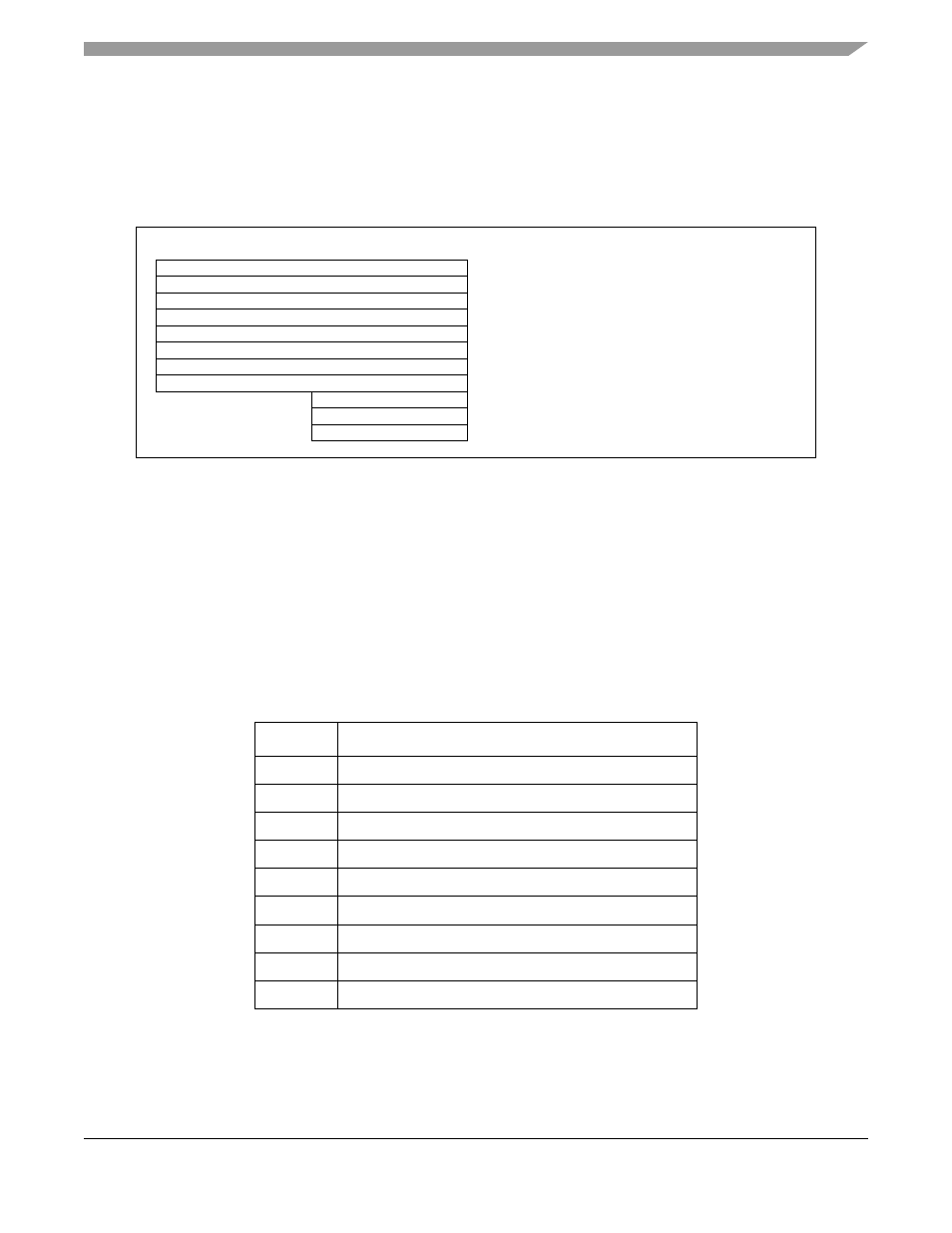

Figure 3-6. Floating-Point Programmer’s Model

3.3.5

Supervisor Programming Model

The MCF548x supervisor programming model is shown in

. Typically, system programmers use

the supervisor programming model to implement operating system functions and provide memory and I/O

control. The supervisor programming model provides access to the user registers and additional supervisor

registers, which include the upper byte of the status register (SR), the vector base register (VBR), and

registers for configuring attributes of the address space connected to the Version 4 processor core. Most

supervisor-level registers are accessed by using the MOVEC instruction with the control register

63

31

0

FP0

Floating-point data registers

FP1

FP2

FP3

FP4

FP5

FP6

FP7

FPCR

Floating-point control register

FPSR

Floating-point status register

FPIAR

Floating-point instruction address register

Table 3-2. MOVEC Register Map

Rc[11–0]

Register Definition

0x002

Cache control register (CACR)

0x004

Access control register 0 (ACR0)

0x005

Access control register 1 (ACR1)

0x006

Access control register 2 (ACR2)

0x007

Access control register 3 (ACR3)

0x801

Vector base register (VBR)

0xC04

RAM base address register 0 (RAMBAR0)

0xC05

RAM base address register 1 (RAMBAR1)

0xC0F

Module base address register (MBAR)