7 dma interrupt pending (dipr), 8 dma interrupt mask register (dimr), Dma interrupt pending (dipr) -10 – Freescale Semiconductor MCF5480 User Manual

Page 730: Dma interrupt mask register (dimr) -10

MCF548x Reference Manual, Rev. 3

24-10

Freescale Semiconductor

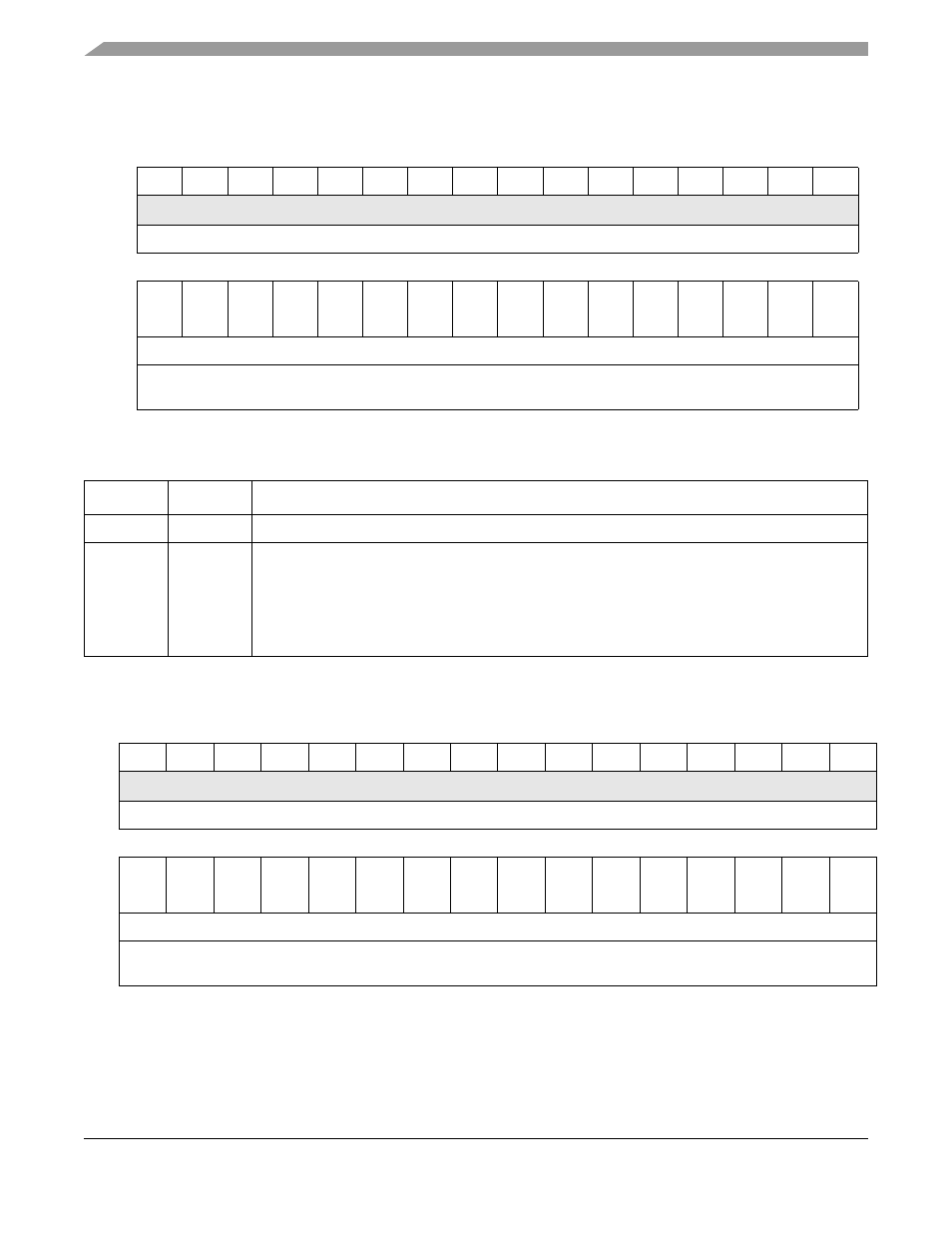

24.3.3.7

DMA Interrupt Pending (DIPR)

24.3.3.8

DMA Interrupt Mask Register (DIMR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R TASK

15

TASK

14

TASK

13

TASK

12

TASK

11

TASK

10

TASK

9

TASK

8

TASK

7

TASK

6

TASK

5

TASK

4

TASK

3

TASK

2

TASK

1

TASK

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR +0x8014

Figure 24-8. DMA Interrupt Pending Register (DIPR)

Table 24-7. DIPR Field Descriptions

Bits

Name

Description

31–16

—

Reserved

15–0

TASKn

Interrupt Pending. Each bit corresponds to an interrupt source defined by the task number. The

corresponding bit in this register reflects the state of the interrupt signal even if the corresponding

mask bit is set. A bit is cleared by writing a 1 to that bit location; writing a zero has no effect. At

system reset, all bits are initialized to logic zeros.

0 The corresponding interrupt source not pending

1 The corresponding interrupt source pending

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R TASK

15

TASK

14

TASK

13

TASK

12

TASK

11

TASK

10

TASK

9

TASK

8

TASK

7

TASK

6

TASK

5

TASK

4

TASK

3

TASK

2

TASK

1

TASK

0

W

Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Reg

Addr

MBAR + 0x8018

Figure 24-9. DMA Interrupt Mask Register (DIMR)