8 master error address register (mear), 7 channels, Master error address register (mear) -18 – Freescale Semiconductor MCF5480 User Manual

Page 620: Channels -18, P. 22-18

MCF548x Reference Manual, Rev. 3

22-18

Freescale Semiconductor

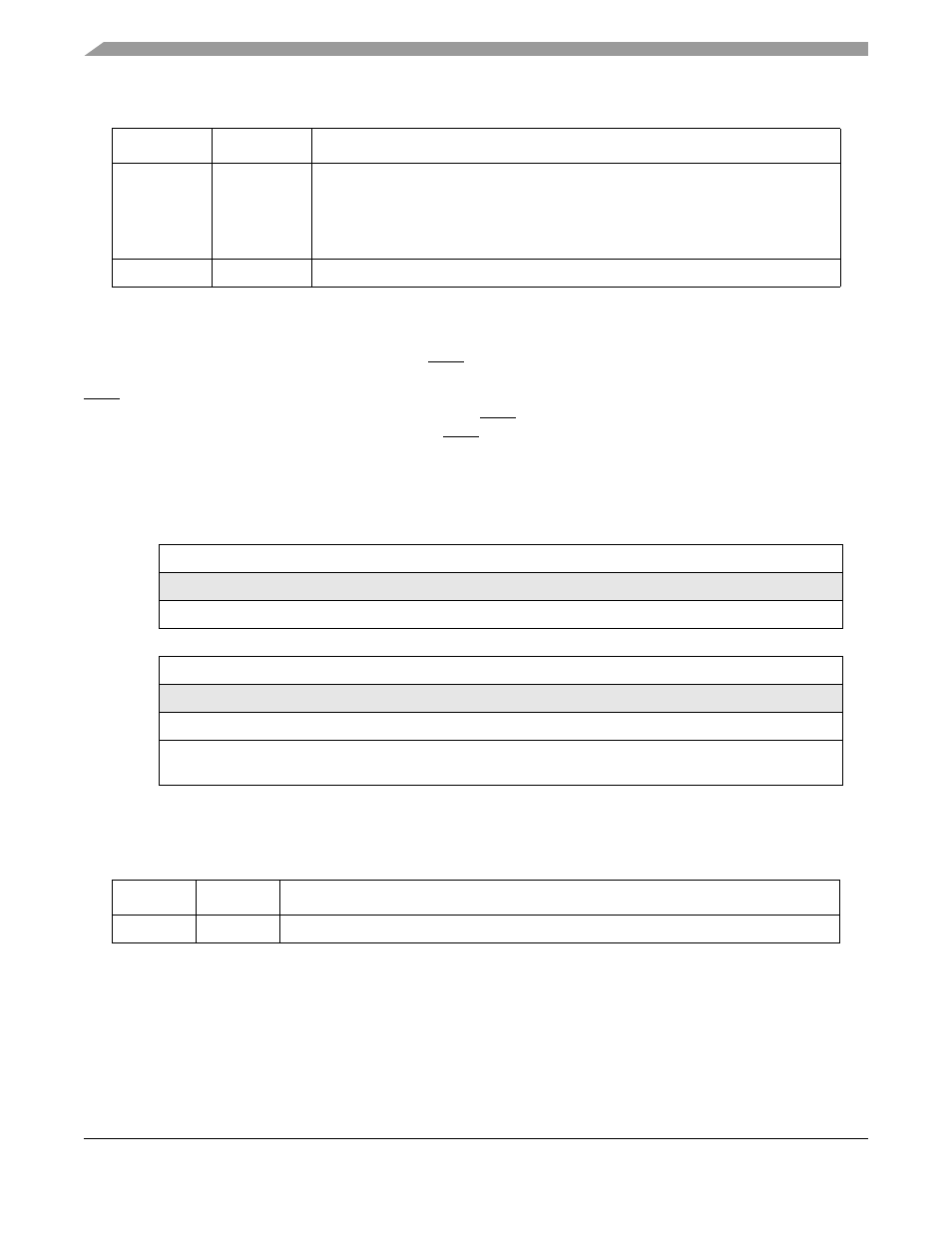

22.6.4.8

Master Error Address Register (MEAR)

This register saves the address of the transaction whose data phase was terminated with a TEA or Master

Parity Error. A Transfer Error Acknowledge (TEA) signal indicates a fatal error has occurred during the

data phase of a bus transaction. Invalid data may have been received and stored prior to the receipt of the

TEA. The channel that was initiating the transaction will be evident from that channel’s error interrupt.

Software may chose to reset the channel reporting the TEA, reset the whole SEC, or reset the entire system.

In any case, the host may chose to preserve this TEA information prior to reset to assist in debug.

The MEAR only holds the address of the first error reported, in the event multiple errors are received

before the first is cleared.

22.7

Channels

A crypto-channel manages data associated with the one or more execution units (EUs). Control and data

information for a given task is stored in the form of data packet descriptors in system memory. The

descriptor describes how the EU should be initialized, where to fetch the data to be ciphered and where to

7–4

CURR_CHAN Current Channel. These bits are read only. They indicate the channel number that is

currently in use by the controller as a master on the XLB bus. The possible values are:

0000 - No Channel is currently in use.

0001 - Channel 0 is in use.

0010 - Channel 1 is in use.

3–0

—

Reserved

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Address

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Address

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x 21038

Figure 22-15. Master Error Address Register (MEAR)

Table 22-10. MEAR Field Descriptions

Bits

Name

Description

31–0

ADDRESS Target address of the transaction when TEA was received.

Table 22-9. SMCR Field Descriptions (Continued)

Bits

Name

Description