6 repeated start, 7 clock synchronization and arbitration, Repeated start -11 – Freescale Semiconductor MCF5480 User Manual

Page 865: Clock synchronization and arbitration -11, Refer to, Section 28.4.6, “repeated start, Figure 28-11, To start a new

Functional Description

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

28-11

28.4.6

Repeated Start

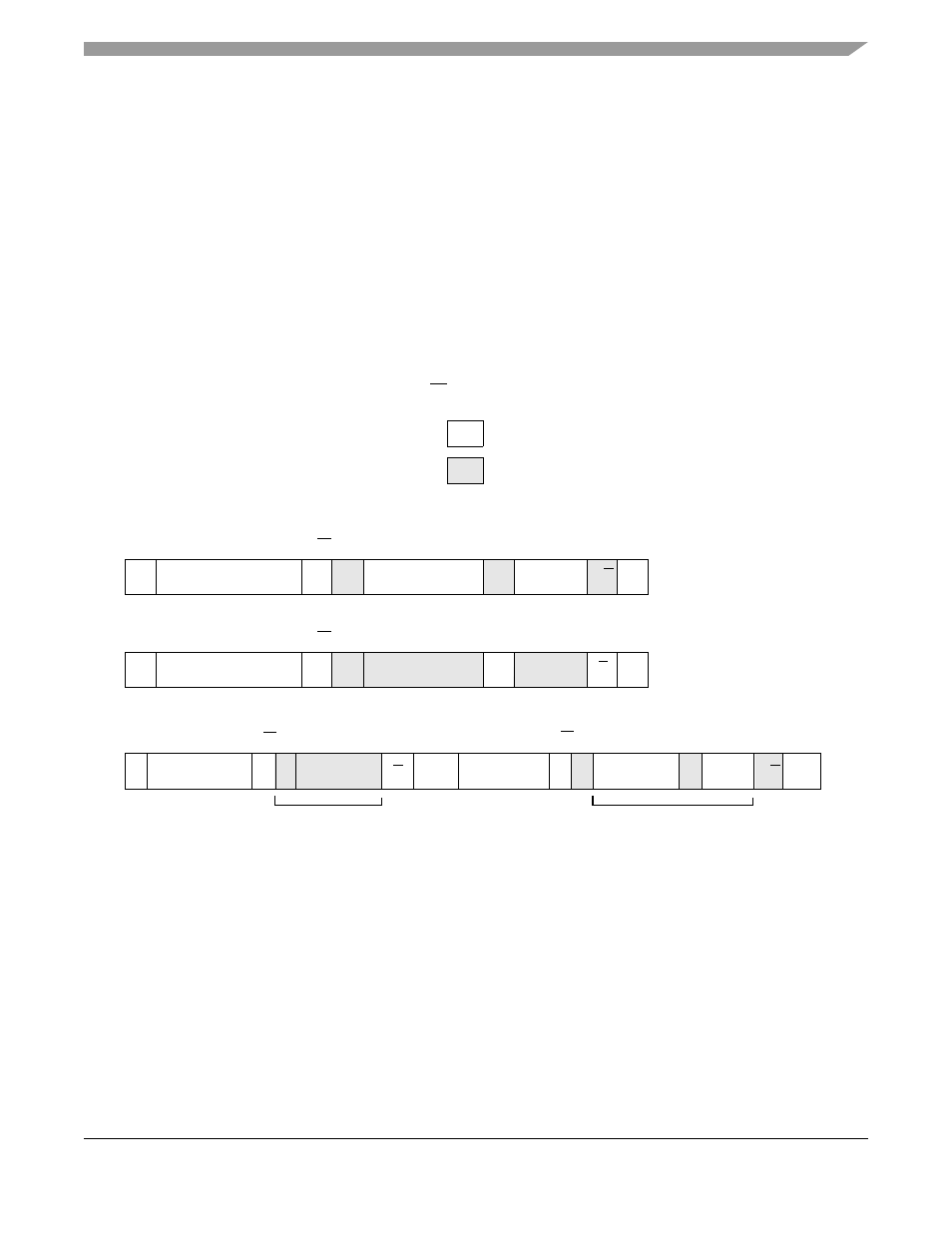

A repeated START signal is a START signal generated without first generating a STOP signal to terminate

the communication. This is used by the master to communicate with another slave or with the same slave

in a different mode without releasing the bus.

Various combinations of read/write formats are then possible:

•

is the case of a master-transmitter transmitting to a

slave-receiver. The transfer direction is not changed.

•

The second example in

is the master reading slave data immediately after the first

byte. At the moment of the first acknowledge, the master-transmitter becomes a master-receiver

and the slave-receiver becomes a slave-transmitter.

•

, the START condition and slave address are both repeated

using the repeated START signal. This is to communicate with the same slave in a different mode

without releasing the bus. The master transmits data to the slave first, and then the master reads

data from the slave by reversing the R/W bit.

Figure 28-11. Data Transfer, Combined Format

28.4.7

Clock Synchronization and Arbitration

I

2

C is a true multi-master bus that allows more than one master to be connected to it. If two or more masters

try to control the bus at the same time, a clock synchronization procedure determines the bus clock.

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all

the devices connected on the bus. The devices start counting their low period. Once a device’s clock has

gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to

high in this device clock may not change the state of the SCL line if another device clock is still within its

low period. Therefore, synchronized clock SCL is held low by the device with the longest low period.

ST

A

7-bit Slave Address

0

A

DATA

DATA

A/A

R/W

SP

From Master to Slave

From Slave to Master

ST = Start

SP = Stop

A = Acknowledge (SDA low)

A = Not Acknowledge (SDA high)

ST

A

7-bit Slave Address

1

A

DATA

DATA

A

R/W

SP

ST

A

1

A

DATA

R/W

Rept

A

7-bit Slave 0

A

DATA

DATA

A/A

R/

W

SP

Rept ST = Repeated Start

ST

Address

7-bit Slave

Address

Example 1:

Example 2:

Example 3:

Master Reads from Slave

Master Writes to Slave

Note: No acknowledge on the last byte.