4 sdram ddr dimm connections, Sdram ddr dimm connections -7, Figure 18-3 – Freescale Semiconductor MCF5480 User Manual

Page 455: Shows a block diagram of the

Interface Recommendations

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

18-7

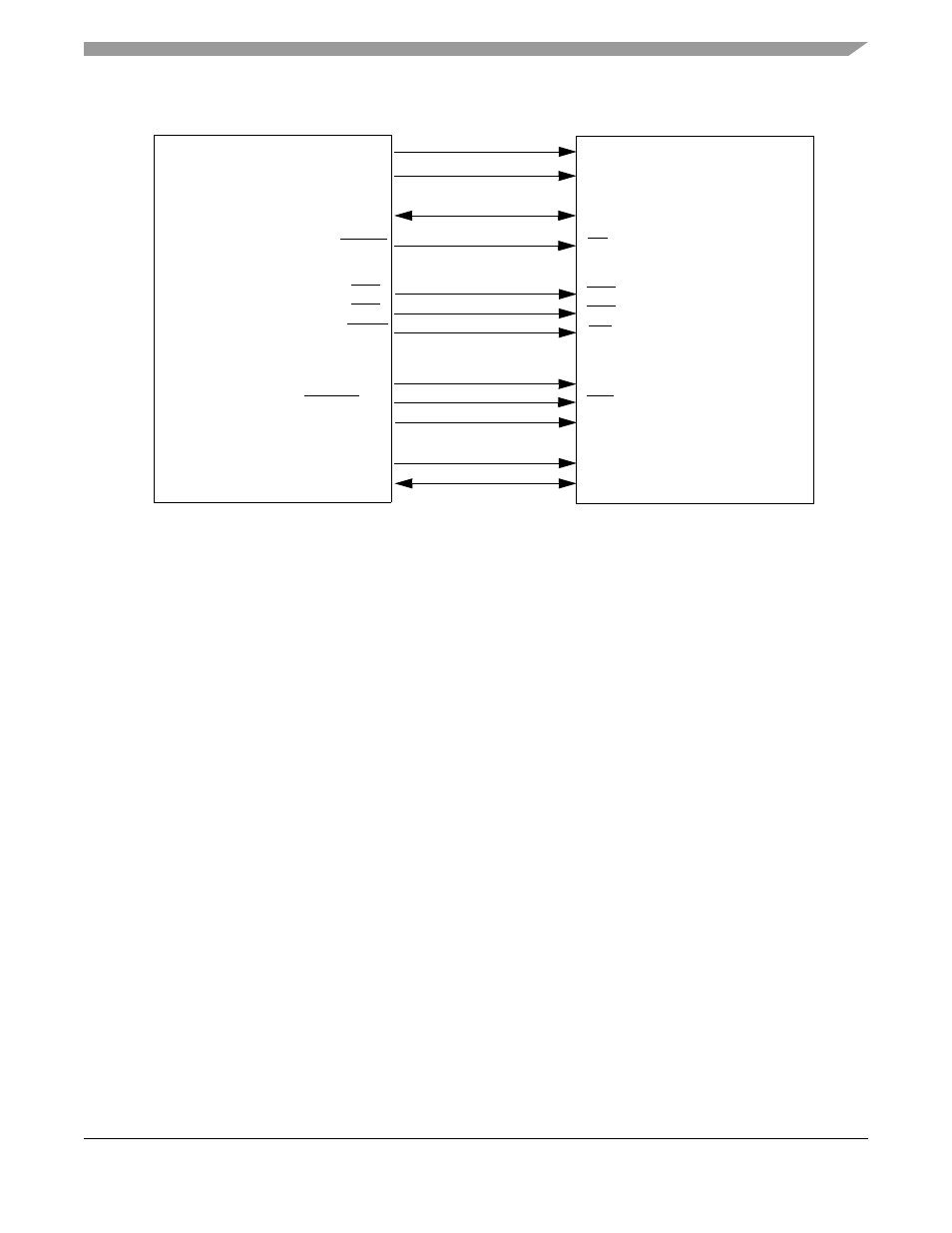

Figure 18-3. MCF548x Connections to DDR SDRAM

18.4.4

SDRAM DDR DIMM Connections

There is a JEDEC standard for a 100-pin DDR DIMM with a 32-bit wide data bus. This DIMM standard

was designed specifically to support 32-bit processors. The MCF548x can support current DIMM

configurations up to 512 Mbytes.

Figure

shows a block diagram of the connections between the MCF548x and DDR SDRAM DIMMs.

MCF548X

DDR SDRAM

SD_CKE

SD_CLK[1:0]

SD_CLK[1:0]

SDDM[3:0]

SDDQS[3:0]

CLK

CLK

CKE

CS

RAS

CAS

WE

DM[3:0]

BA[1:0]

A[12:0]

DQ[31:0]

DQS[3:0]

SDADDR[12:0]

SDDATA[31:0]

SDBA[1:0]

SDCSn

RAS

CAS

SDWE