Freescale Semiconductor MCF5480 User Manual

Page 54

MCF548x Reference Manual, Rev. 3

liv

Freescale Semiconductor

Add the following table below the note at the end of the section and correct the cross-reference pointing to

it:

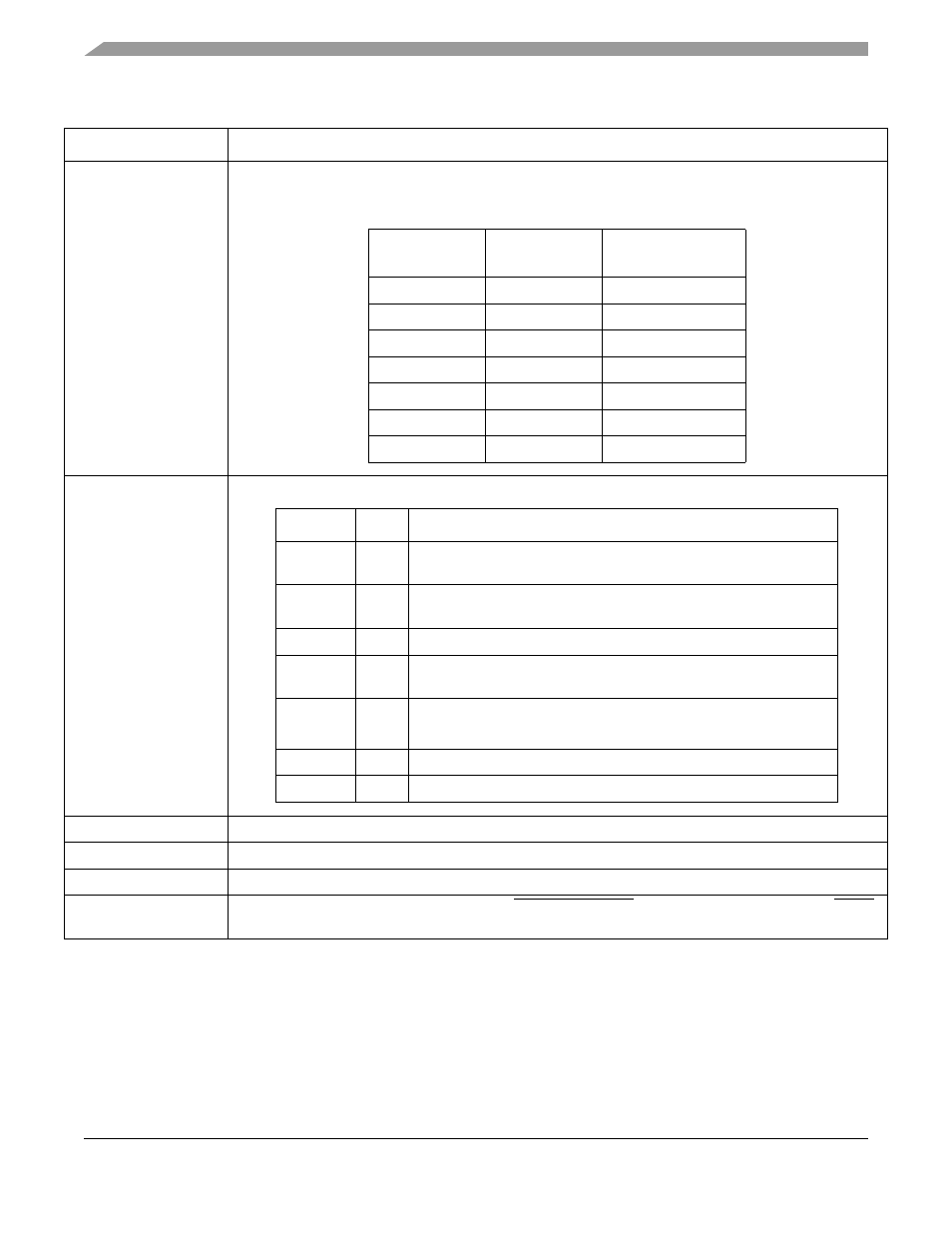

The JTAG IR codes are incorrect. Replace table with the following:

Remove the TEST_LEAKAGE section, as the instruction is not supported.

Remove the LOCKOUT_RECOVERY section, as the instruction is not supported.

Correct Base Address Mask Register 1 mnemonic from EREQMASK0 to EREQMASK1.

Correct overbar in first sentence. From “After DREQ is asserted, this register contains...” to “After DREQ

is asserted, this register contains...”

Table iv. MCF548x Revision History (continued)

Section/Page

Substantive Changes

Table 21-19. CAN Standard Compliant Bit Time Segment Settings

Time Segment 1

Time Segment 2

Re-synchronization

Jump Width

5 .. 10

2

1 .. 2

4 .. 11

3

1 .. 3

5 .. 12

4

1 .. 4

6 .. 13

5

1 .. 4

7 .. 14

6

1 .. 4

8 .. 15

7

1 .. 4

9 .. 16

8

1 .. 4

F

Instruction IR[5:0]

Instruction Summary

EXTEST

000000 Selects boundary scan register while applying fixed values to output

pins and asserting functional reset

SAMPLE

000001 Selects boundary scan register for shifting, sampling, and preloading

without disturbing functional operation

IDCODE

011101 Selects IDCODE register for shift

CLAMP

011111 Selects bypass while applying fixed values to output pins and

asserting functional reset

HIGHZ

111101 Selects bypass register while tri-stating all output pins and asserting

functional reset

ENABLE

000010 Selects TEST_CTRL register

BYPASS

111111 Selects bypass register for data operations