20 infrared fir divide register (pscirfdrn), Infrared fir divide register (pscirfdrn) -26, 20 infrared fir divide register (pscirfdr n ) – Freescale Semiconductor MCF5480 User Manual

Page 788: This register sets the baud rate in fir mode

MCF548x Reference Manual, Rev. 3

26-26

Freescale Semiconductor

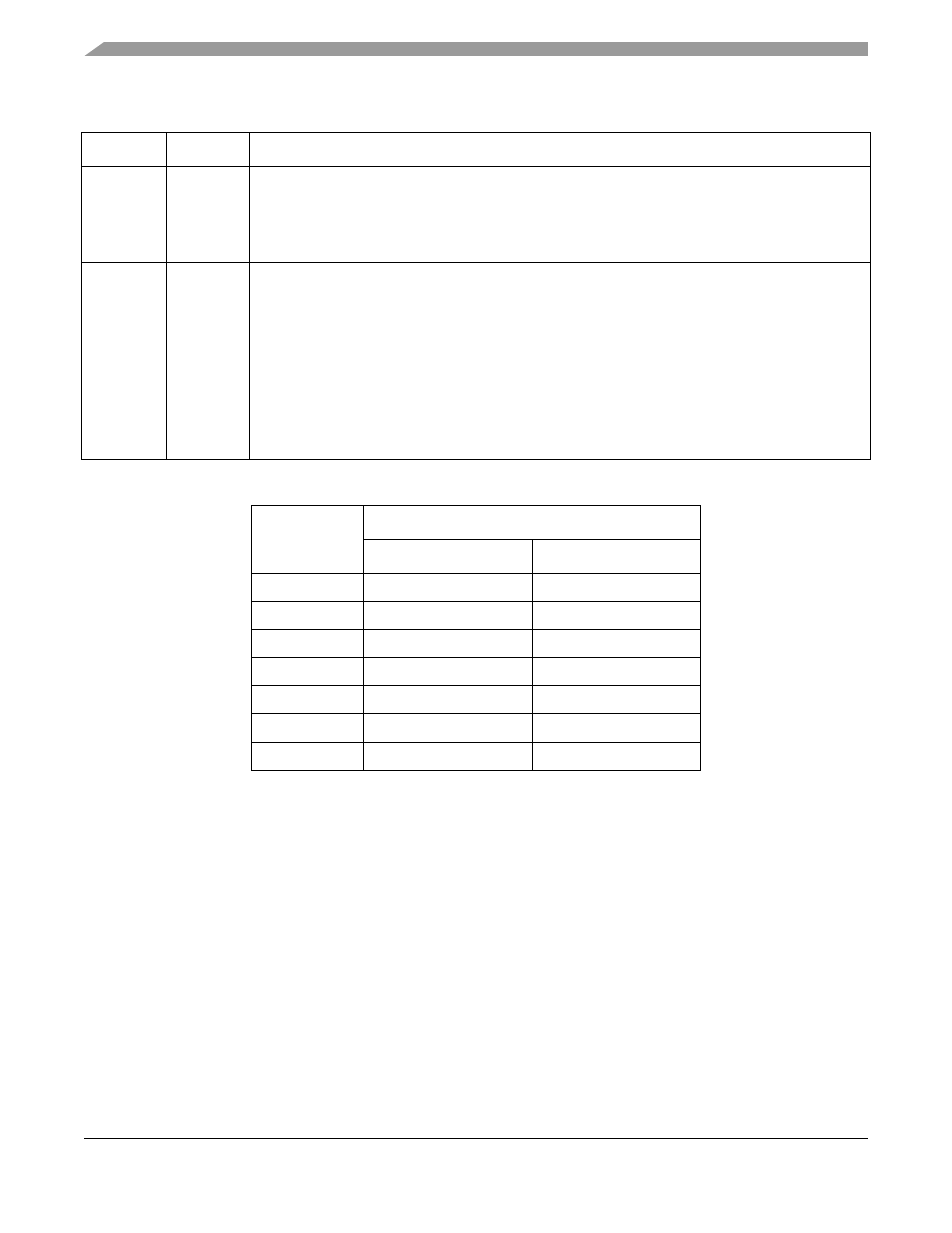

26.3.3.20 Infrared FIR Divide Register (PSCIRFDRn)

This register sets the baud rate in FIR mode.

Table 26-25. PSCIRMDRn Field Descriptions

Bits

Name

Description

7

FREQ

Applies only in MIR mode; in all other modes, this field is reserved.

In MIR mode, this bit signifies 0.576 Mbps mode.

0 The baud rate is 1.152 Mbps.

1 If the baud rate is 0.576 Mbps, this bit should be set high in order to output 1.6 us SIP.

6–0

M_FDIV

Applies only in MIR mode; in all other modes, this field is reserved.

In MIR mode, this bit signifies clock divide ratio. The bit frequency is derived by the following

equation.

Eqn. 26-1

This bit frequency should be 0.576 or 1.152 MHz. In order to send a quarter bit duration pulse and

receive minimum pulse described in the IrDA spec, (M_FDIV + 1) should be a factor of 4 and larger

than or equal to 8.

shows the selectable divide factor and the input clock frequency on

the PSCBCLK port. See

Table 26-26., “Frequency Selection in MIR Mode

Table 26-26. Frequency Selection in MIR Mode

M_FDIV

Frequency of bit_clk [MHz]

1.152 Mbps

0.576 Mbps

7

9.216

4.6080

11

18.432

9.216

15

36.864

18.432

19

73.728

36.864

23

147.46

73.728

27

294.91

147.46

31

589.82

294.91

f

bit

f

bit_clk

M_FDIV 1

+

-------------------------------

=