6 sir mode, 7 mir mode, 1 data format – Freescale Semiconductor MCF5480 User Manual

Page 803: Sir mode -41, Mir mode -41, Data format -41

Functional Description

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

26-41

Leaving low power mode can be done via either a warm or cold reset (

a warm reset by writing a 1 to the AWR bit of SICR register for a minimum of 1 us. The AWR bit forces

a 1 on PSCnRTS, which is used as the frame sync output in AC97 mode. The pulse width of warm or cold

reset should be dependent on AC97 codec chip.

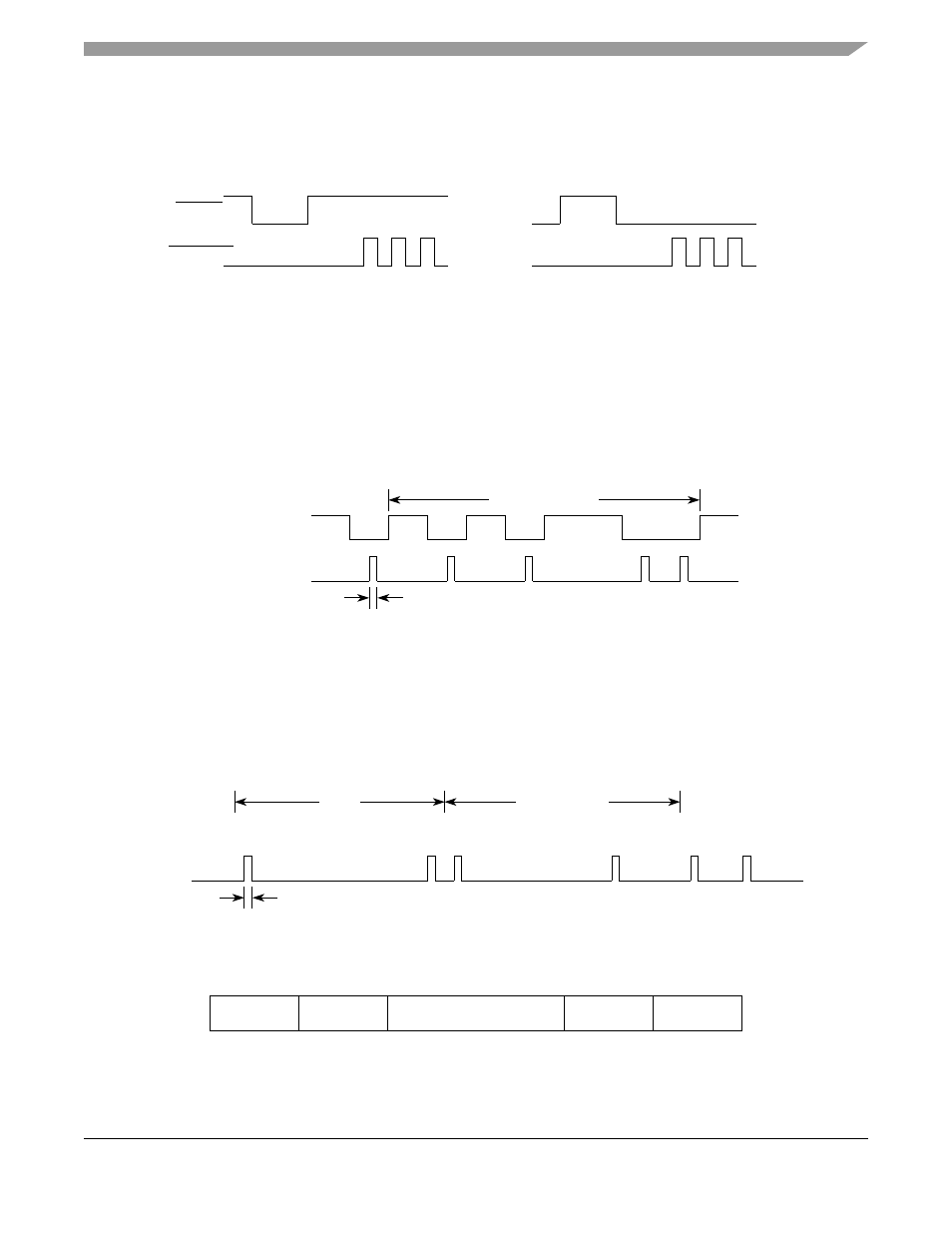

Figure 26-34. AC97 Cold and Warm Reset

26.4.6

SIR Mode

The data format in SIR mode is similar to that of UART mode. Each data consists of a start bit, 8 bit data,

and a stop bit. Each bit of data is encoded so that a 0 is encoded as 3/16 of the bit time pulse (or 1.6

υs

pulse), and a 1 is encoded as no pulse. Similarly, the received serial pulse is decoded as a 0, and an absence

of a pulse is decoded as a 1.

is an example of data stream of UART and SIR.

Figure 26-35. Data Format in SIR Mode

26.4.7

MIR Mode

26.4.7.1

Data Format

The encoded pulse width of data in MIR mode is 1/4 of the bit duration and the transfer is synchronous.

Figure 26-36. Data Format in MIR Mode

The packet format is similar to HDLC packet format

Figure 26-37. MIR Packet Format

Cold reset

Warm reset

RESET

PSCBCLK

PSCFSYNC

PSCBCLK

UART Data Format

3/16 of the bit width or 1.6 µs

0

1

0

1

0

1

1

1

0

0

SIR Data Format

Data Bits (8-bit)

START Bit

STOP Bit

Binary Data

1/4 of the bit width

0

1

1

1

1

1

1

1

0

0

1

1

1

1

0

1

0

1

0

1

1

Flag

Character FE

STA

STA

FCS

STO

DATA

01111110

01111110

16-bit CRC

01111110