1 interrupt sources – Freescale Semiconductor MCF5480 User Manual

Page 364

MCF548x Reference Manual, Rev. 3

13-12

Freescale Semiconductor

13.2.1.6.1

Interrupt Sources

lists the interrupt sources for each interrupt request line

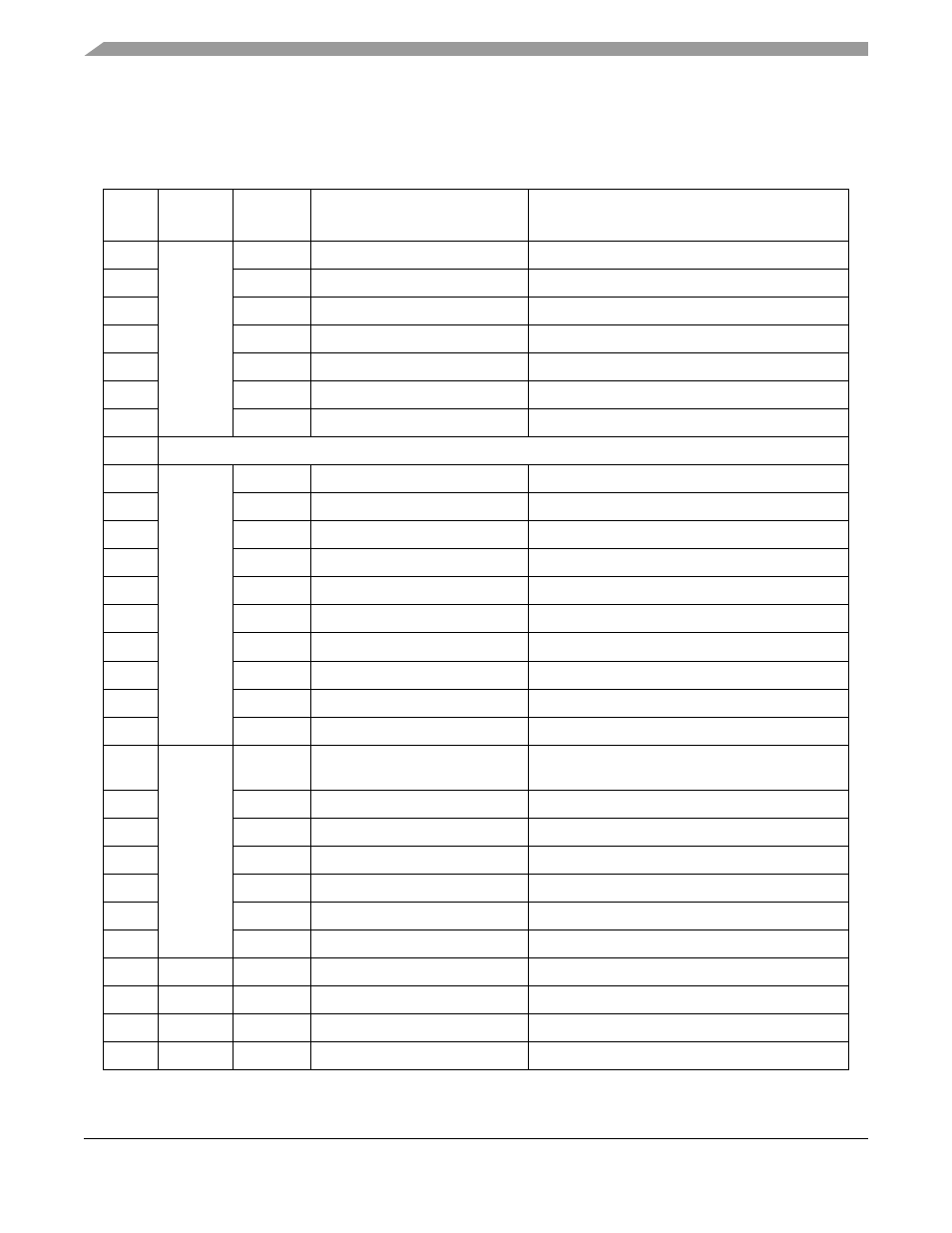

Table 13-12. Interrupt Source Assignments

Sourc

e

Module

Flag

Source Description

Flag Clearing Mechanism

1

EPORT

EPF1

Edge port flag 1

Write ‘1’ to EPFR[EPF1]

2

EPF2

Edge port flag 2

Write ‘1’ to EPFR[EPF2]

3

EPF3

Edge port flag 3

Write ‘1’ to EPFR[EPF3]

4

EPF4

Edge port flag 4

Write ‘1’ to EPFR[EPF4]

5

EPF5

Edge port flag 5

Write ‘1’ to EPFR[EPF5]

6

EPF6

Edge port flag 6

Write ‘1’ to EPFR[EPF6]

7

EPF7

Edge port flag 7

Write ‘1’ to EPFR[EPF7]

8–14

Not used

15

USB 2.0

EP0ISR

Endpoint 0 interrupt

Write ‘1’ to appropriate bit in EP0ISR

16

EP1ISR

Endpoint 1 interrupt

Write ‘1’ to appropriate bit in EP1ISR

17

EP2ISR

Endpoint 2 interrupt

Write ‘1’ to appropriate bit in EP2ISR

18

EP3ISR

Endpoint 3 interrupt

Write ‘1’ to appropriate bit in EP3ISR

19

EP4ISR

Endpoint 4 interrupt

Write ‘1’ to appropriate bit in EP4ISR

20

EP5ISR

Endpoint 5 interrupt

Write ‘1’ to appropriate bit in EP5ISR

21

EP6ISR

Endpoint 6 interrupt

Write ‘1’ to appropriate bit in EP6ISR

22

USBISR

USB 2.0 general interrupt

Write ‘1’ to appropriate bit in USBISR

23

USBAISR USB 2.0 core interrupt

Write ‘0’ to appropriate bit in USBAISR

24

—

OR of all USB interrupts

Clear appropriate USB interrupt(s)

25

DSPI

RFOF |

TFUF

DSPI overflow or underflow

Write ‘1’ to DSR[RFDF] and/or DSR[TFUF]

26

RFOF

Receive FIFO overflow interrupt

Write ‘1’ to DSR[RFOF]

27

RFDF

Receive FIFO drain interrupt

Write ‘1’ to DSR[RFDF] or DMA acknowledge

28

TFUF

Transmit FIFO underflow interrupt Write ‘1’ to DSR[TFUF]

29

TCF

Transfer complete interrupt

Write ‘1’ to DSR[TCF]

30

TFFF

Transfer FIFO fill interrupt

Write ‘1’ to DSR[TFFF] or DMA acknowledge

31

EOQF

End of queue interrupt

Write ‘1’ to DSR[EOQF]

32

PSC3

—

PSC3 interrupt

Cleared when service complete

33

PSC2

—

PSC2 interrupt

Cleared when service complete

34

PSC1

—

PSC1 interrupt

Cleared when service complete

35

PSC0

—

PSC0 interrupt

Cleared when service complete