7 instructions, 1 floating-point instruction overview, Instructions -25 – Freescale Semiconductor MCF5480 User Manual

Page 215: Floating-point instruction overview -25, Table 6-23

Instructions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

6-25

Normally, an exception handler executes FSAVE, processes the exception, clears the exception bit in the

FSAVE state frame status word, and executes FRESTORE. If appropriate exception bits set in the status

word are not cleared, the same exception is taken again. If multiple exception bits are set in the status word,

each should be processed, cleared, and restored by their respective handlers. In this way, all exceptions are

processed in priority order.

If it is not necessary to handle multiple exceptions, the exception model can be simplified (after any

processing) by the handler manually loading FPCR and FPSR and then discarding the state frame before

executing an RTE. Given that state frames are four longwords, it may be quicker to discard the state frame

by incrementing the address pointer (often the system stack pointer, A7) by 16.

The exception operand, contained in longwords two and three of the FSAVE frame, is always the value of

the destination operand before the operation which caused the exception commenced. Thus, for dyadic

register-to-register operations, the exception operand contains the value of the destination register before

it was overwritten by the operation which caused the exception. This operand can be retrieved by an

exception handler that needs both original operands in order to process the exception.

6.7

Instructions

This section includes an instruction set summary, execution times, and differences between ColdFire and

M68000 FPU programming models. For detailed instruction descriptions, see the ColdFire Programmer’s

Reference Manual.

6.7.1

Floating-Point Instruction Overview

ColdFire instructions are 16-, 32-, or 48-bits long. The general definition of a floating-point operation and

effective addressing mode require 32 bits; some addressing modes require another 16-bit extension word.

shows the minimum size instruction formats. The first word is the opword; the second is

extension word 1.

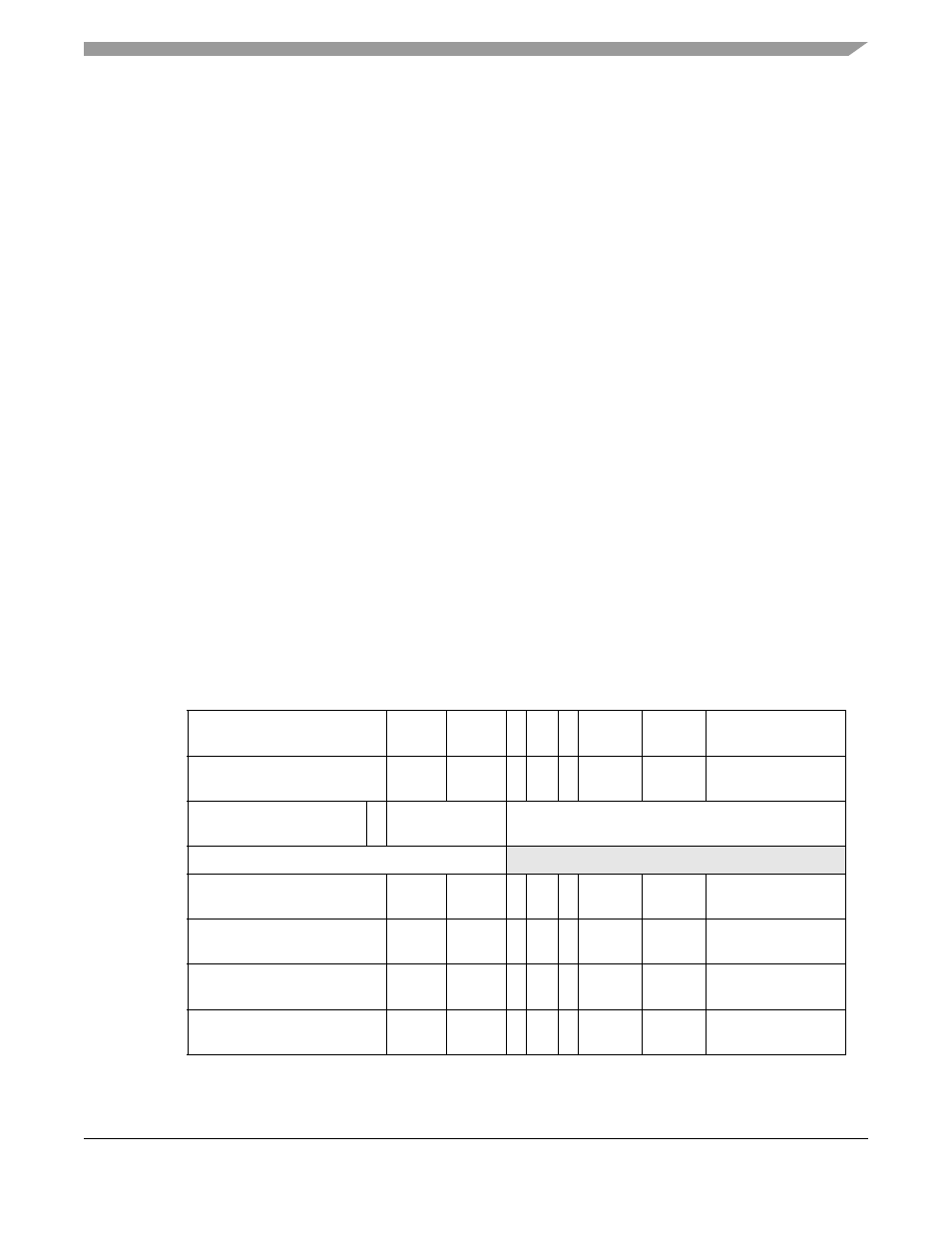

Table 6-23. Floating-Point Instruction Formats

Mnemonic

Instruction Code

FABS

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FADD

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FBcc

1 1 1 1 0 0 1 0 1 s

z

cond predicate

16b displacement or MS Word of 32b

LS Word of 32b Displacement

FCMP

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg 0 1 1 1 0 0 0

FDIV

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg

opmode

FINT

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg 0 0 0 0 0 0 1

FINTRZ

1 1 1 1 0 0 1 0 0 0

ea

mode

ea reg

0 r/m 0 src spec dest reg 0 0 0 0 0 1 1