Freescale Semiconductor MCF5480 User Manual

Page 564

MCF548x Reference Manual, Rev. 3

20-4

Freescale Semiconductor

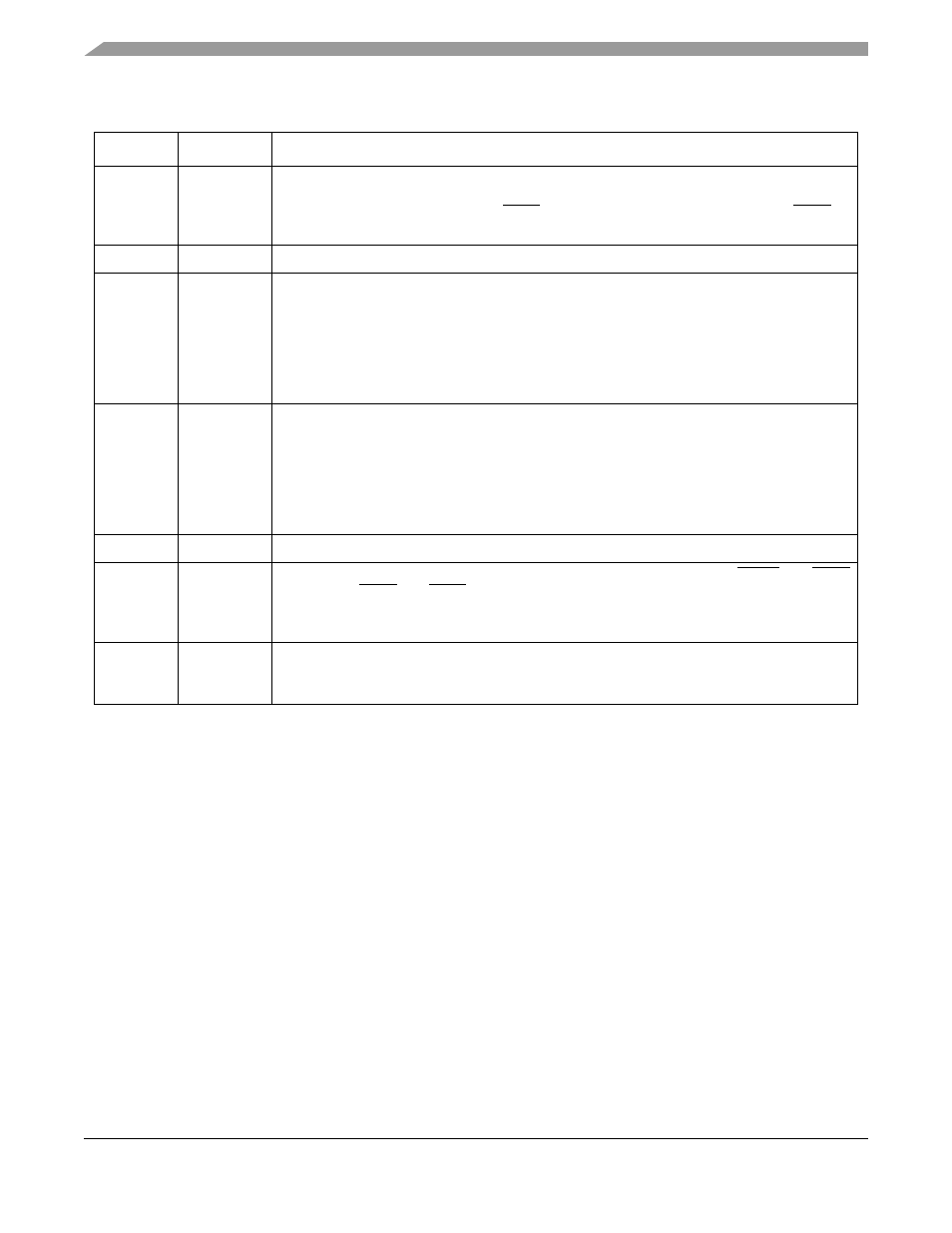

Table 20-2. PACR Field Descriptions

Bits

Name

Description

31

DS

Disable bit for the internal PCI arbiter.

0 Enable the PCI arbiter.

1 Disable the on-chip arbiter and use GNT0 for the MCF548x PCI request output and REQ0 for

its grant input.

30–22

—

Reserved, should be cleared.

21–17

EXTMINTEN External master broken interrupt enables. If an external master time-out occurs and the

corresponding interrupt enable bit is set, a CPU interrupt will be generated. Bit 21 is the enable

for PASR bit 21, bit 20 for PASR bit 20, and so on.

0 Disable interrupt

1 Enable interrupt

Software must write 1 to the asserted external master broken bit(s) in PASR to clear the

interrupt condition.

16

INTMINTEN

Internal master broken interrupt enable for the MCF548x master time-out status bit internal

master broken (bit 16 of the PASR). If an MCF548x master time-out occurs and this bit is set,

a CPU interrupt will be generated.

0 Disable interrupt

1 Enable interrupt

Software must write 1 to the asserted internal master broken bit in PASR to clear the interrupt

condition.

15–6

—

Reserved. Software should write zero to this register.

5–1

EXTMPRI

External master priority levels. Bit 1 controls the priority for the device using REQ[0] and GNT0

pins, bit 2 for REQ1 and GNT1, etc.

0 Low

1 High

0

INTMPRI

Internal master priority level.

0 Low

1 High