31 fec transmit fifo alarm register (fectfar), Fec transmit fifo alarm register (fectfar) -39 – Freescale Semiconductor MCF5480 User Manual

Page 969

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

30-39

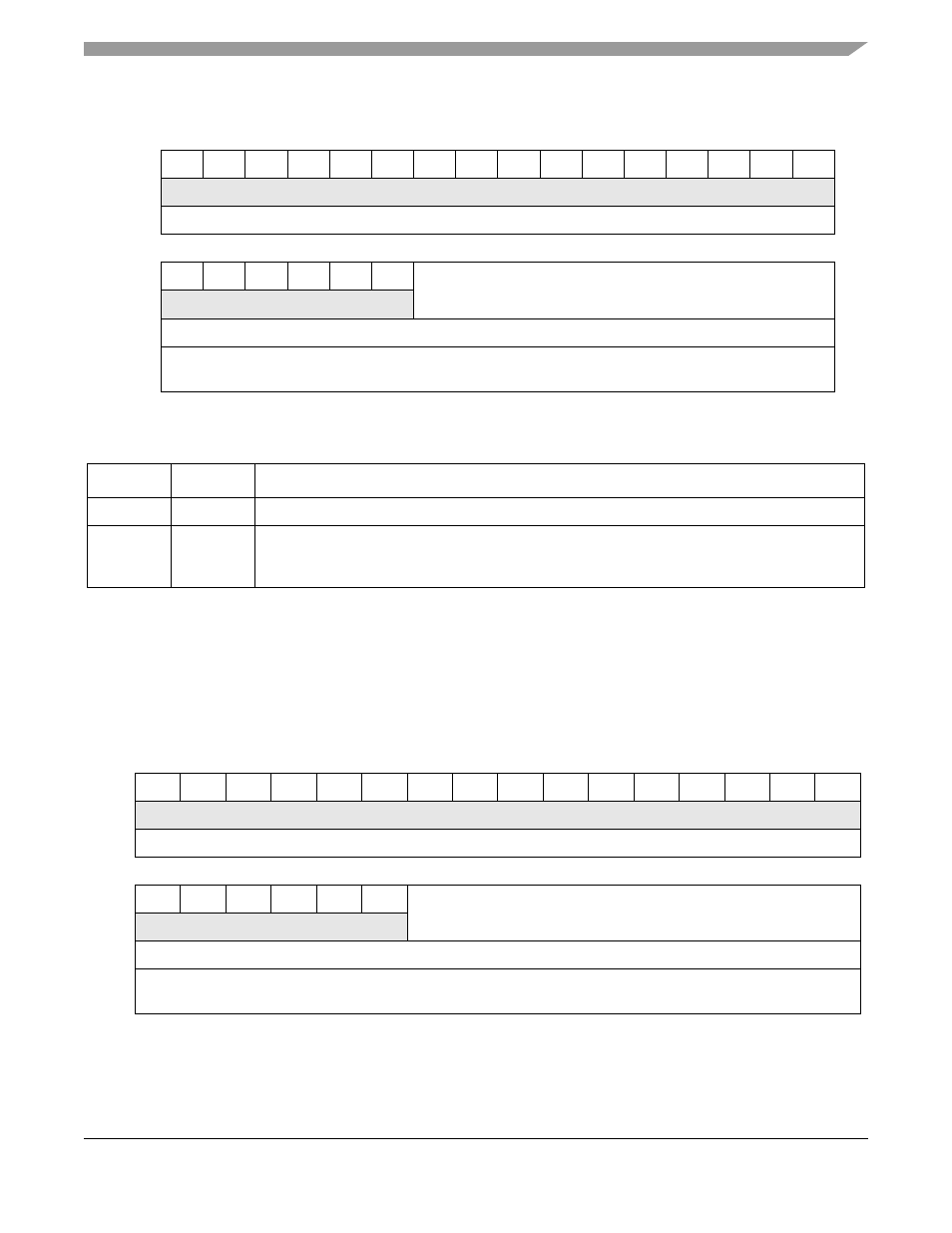

30.3.3.31 FEC Transmit FIFO Alarm Register (FECTFAR)

This pointer provides low level alarm information to the user and the comm bus interface. A low level

alarm reports lack of data. The alarm register defines the alarm threshold for the number of bytes in the

FIFO. If there are less than or equal FECTFAR[ALARM] bytes of data in the FIFO, the

FECTFSR[ALARM] bit is set.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

LWFP

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x91B4 (FEC0), 0x99B4 (FEC1)

Figure 30-33. FEC Transmit FIFO Last Write Frame Pointer Register (FECTLWFP)

Table 30-37. FECTLWFP Field Descriptions

Bits

Name

Descriptions

31–10

—

Reserved, should be cleared.

9–0

LWFP

Last write frame pointer. This pointer indicates the location of the next byte after the last frame that

has been completely written. If no frames have been read out of the FIFO, LWFP indicates the first

byte location in the FIFO( the reset state).

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

ALARM

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x91B8 (FEC0), 0x99B8 (FEC1)

Figure 30-34. FEC Transmit FIFO Alarm Register (FECTFAR)