Freescale Semiconductor MCF5480 User Manual

Page 489

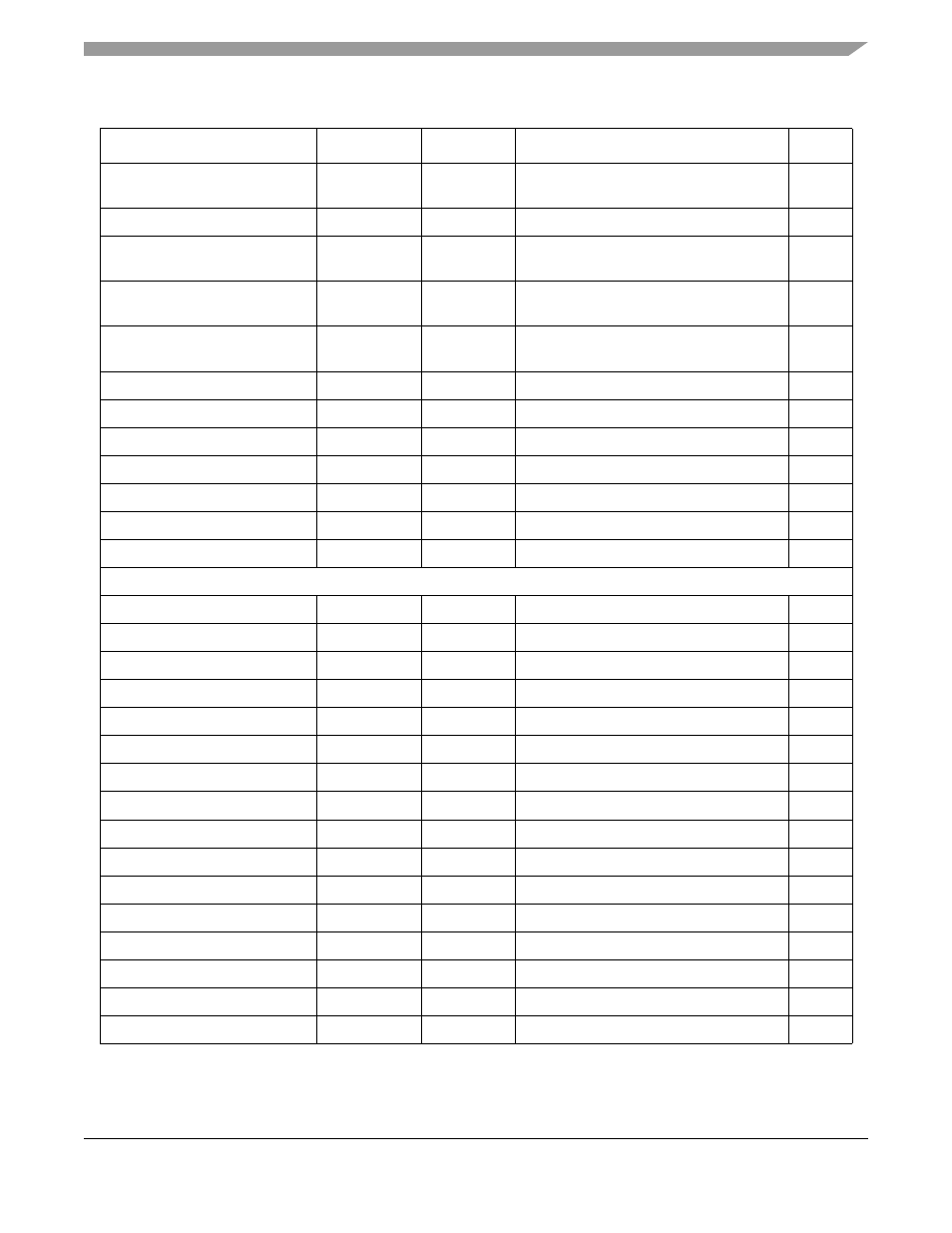

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-5

MBAR + 0xB68

PCITBATR1

32

Target Base Address Translation Register

1

R/W

MBAR + 0xB6C

PCITCR

32

Target Control Register

R/W

MBAR + 0xB70

PCIIW0BTAR

32

Initiator Window 0 Base/Translation

Address Register

R/W

MBAR + 0xB74

PCIIW1BTAR

32

Initiator Window 1 Base/Translation

Address Register

R/W

MBAR + 0xB78

PCIIW2BTAR

32

Initiator Window 2 Base/Translation

Address Register

R/W

MBAR + 0xB7C

—

—

Reserved

—

MBAR + 0xB80

PCIIWCR

32

Initiator Window Configuration Register

R/W

MBAR + 0xB84

PCIICR

32

Initiator Control Register

R/W

MBAR + 0xB88

PCIISR

32

Initiator Status Register

R/W

MBAR + 0xB8C–0xBF4

—

—

Reserved

—

MBAR + 0xBF8

PCICAR

32

Configuration Address Register

R/W

MBAR + 0xBFC

—

—

Reserved

—

CommBus FIFO Transmit Interface Registers

MBAR + 0x8400

PCITPSR

32

Tx Packet Size Register

R/W

MBAR + 0x8404

PCITSAR

32

Tx Start Address Register

R/W

MBAR + 0x8408

PCITTCR

32

Tx Transaction Control Register

R/W

MBAR + 0x840C

PCITER

32

Tx Enables Register

R/W

MBAR + 0x8410

PCITNAR

32

Tx Next Address Register

R

MBAR + 0x8414

PCITLWR

32

Tx Last Word Register

R

MBAR + 0x8418

PCITDCR

32

Tx Done Counts Register

R

MBAR + 0x841C

PCITSR

32

Tx Status Register

R/WC

MBAR + 0x8420–0x843C

—

—

Reserved

—

MBAR + 0x8440

PCITFDR

32

Tx FIFO Data Register

R/W

MBAR + 0x8444

PCITFSR

32

Tx FIFO Status Register

R/WC

MBAR + 0x8448

PCITFCR

32

Tx FIFO Control Register

R/W

MBAR + 0x844C

PCITFAR

32

Tx FIFO Alarm Register

R/W

MBAR + 0x8450

PCITFRPR

32

Tx FIFO Read Pointer Register

R/W

MBAR + 0x8454

PCITFWPR

32

Tx FIFO Write Pointer Register

R/W

MBAR + 0x8458–0x847C

—

—

Reserved

—

Table 19-2. PCI Memory Map (Continued)

Address

Name

Size

Description

Access