Freescale Semiconductor MCF5480 User Manual

Page 244

MCF548x Reference Manual, Rev. 3

7-24

Freescale Semiconductor

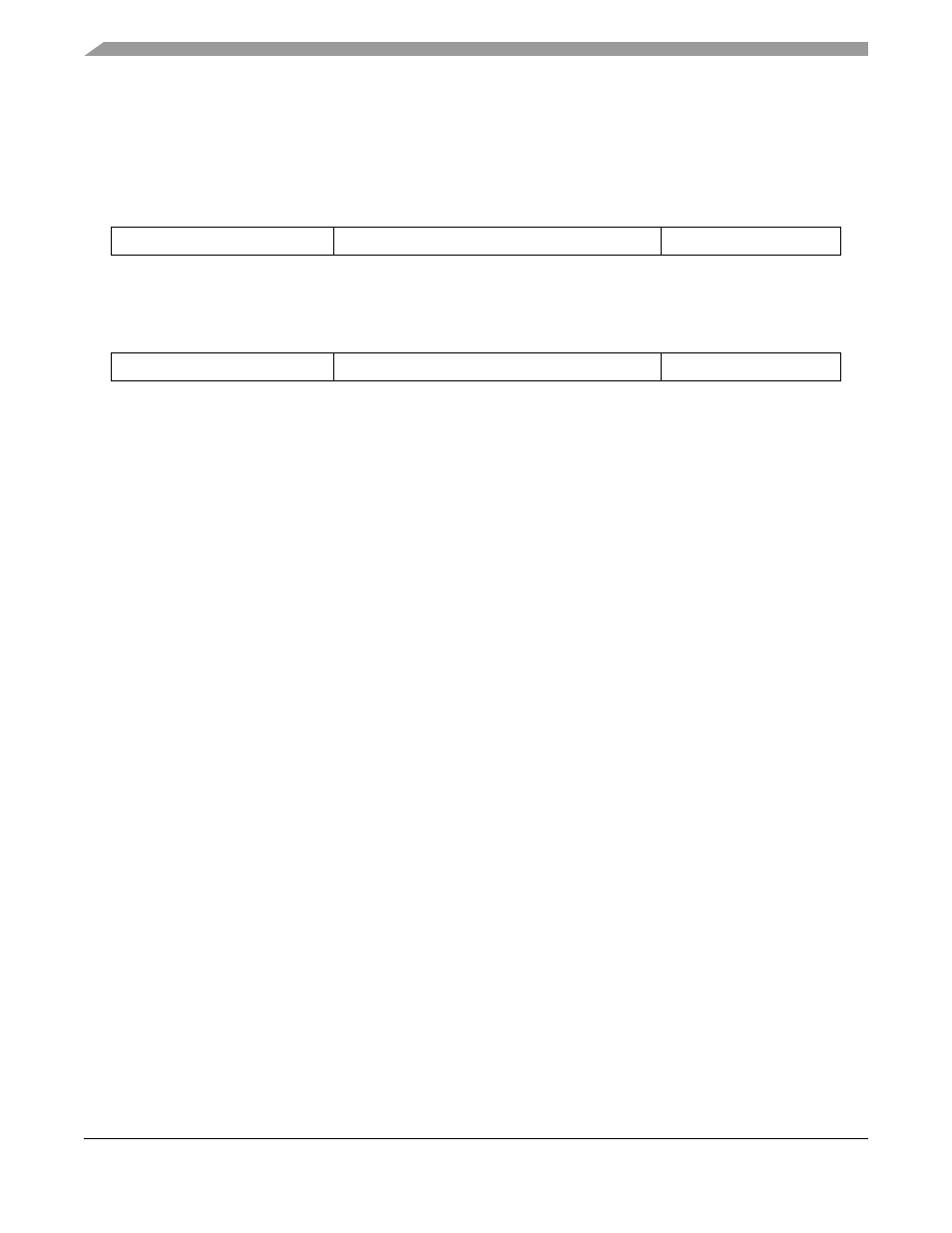

The contents of An used with CPUSHL specify cache row and line indexes. This differs from the 68K

family where a physical address is specified.

shows the An format for the data cache. The

contents of An used with CPUSHL specify cache row and line indexes.

shows the An format for the data cache.

shows the An format for the instruction cache.

The following code example flushes the entire data cache:

_cache_disable:

nop

move.w

#0x2700,SR

;mask off IRQs

jsr

_cache_flush

;flush the cache completely

clr.l

d0

movec

d0,ACR0

;ACR0 off

movec

d0,ACR1

;ACR1 off

move.l

#0x01000000,d0

;Invalidate and disable cache

movec

d0,CACR

rts

_cache_flush:

nop

;synchronize—flush store buffer

moveq.l

#0,d0

;initialize way counter

moveq.l

#0,d1

;initialize set counter

move.l

d0,a0

;initialize cpushl pointer

setloop:

cpushl

dc,(a0)

;push cache line a0

add.l

#0x0010,a0

;increment set index by 1

addq.l

#1,d1

;increment set counter

cmpi.l

#511,d1

;are sets for this way done?

bne

setloop

moveq.l

#0,d1

;set counter to zero again

addq.l

#1,d0

;increment to next way

move.l

d0,a0

;set = 0, way = d0

cmpi.l

#4,d0

;flushed all the ways?

bne

setloop

rts

The following CACR loads assume the instruction cache has been invalidated, the default instruction

cache mode is cacheable, and the default data cache mode is copyback.

31

13

12

4

3

0

0

Set Index

Way Index

Figure 7-10. An Format (Data Cache)

31

13

12

4

3

0

0

Set Index

Way Index

Figure 7-11. An Format (Instruction Cache)