3 arbiter status register (xarb_sr), 4 arbiter interrupt mask register (xarb_imr), Arbiter status register (xarb_sr) -11 – Freescale Semiconductor MCF5480 User Manual

Page 333: Arbiter interrupt mask register (xarb_imr) -11

XL Bus Arbiter

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

10-11

10.3.3.3

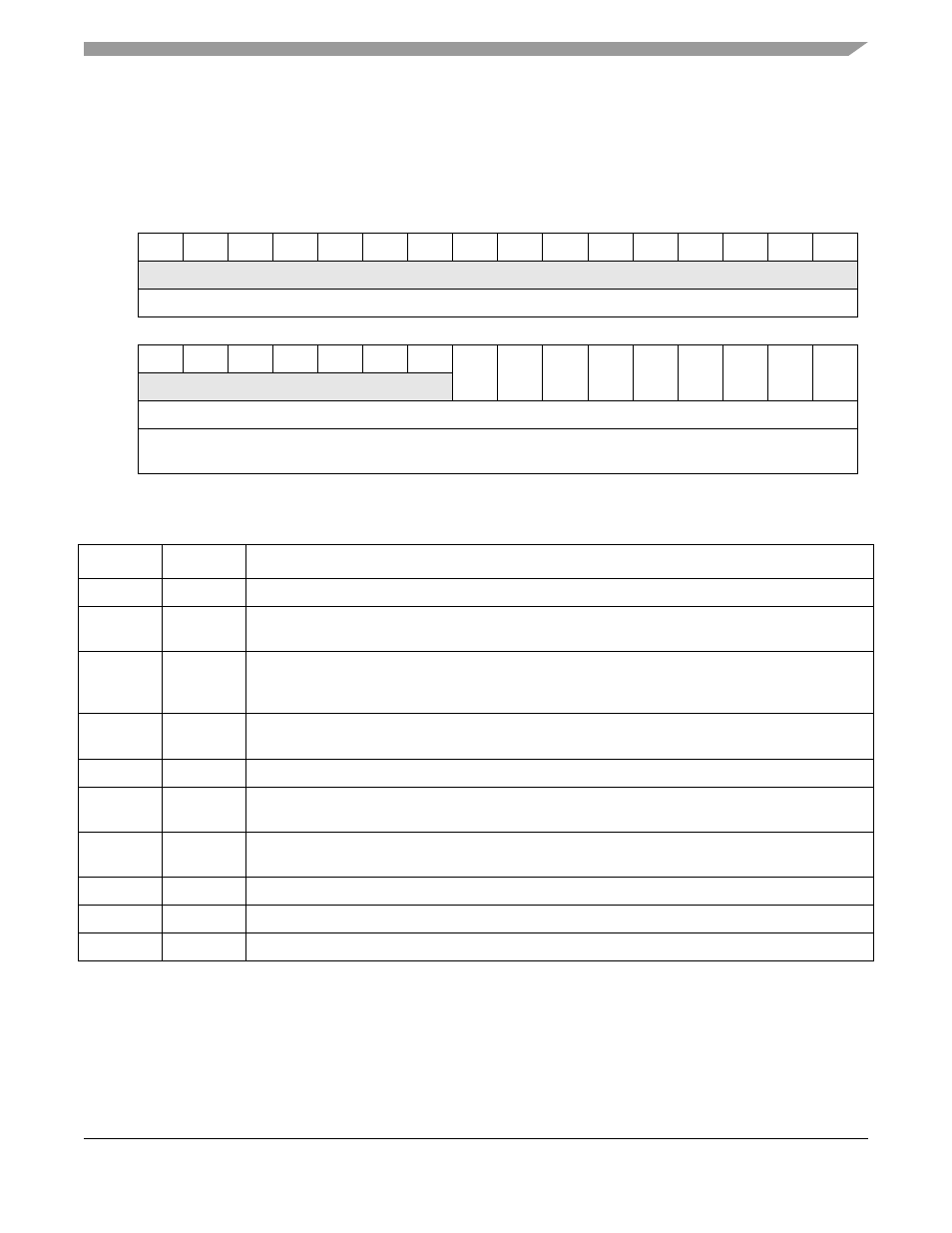

Arbiter Status Register (XARB_SR)

The arbiter status register indicates the state of watchdog functions. When a monitored condition occurs,

the respective bit is set to 1. The bit will stay set until the bit is cleared by writing a 1 into that bit. Even if

the causal condition is removed, the bit will remain set until cleared.

10.3.3.4

Arbiter Interrupt Mask Register (XARB_IMR)

The arbiter interrupt mask register is used to enable a status bit to cause an interrupt. If the interrupt mask

and corresponding status bits are set in the arbiter status register and arbiter interrupt mask register, the

arbiter will assert the interrupt signal. Normally, an interrupt service routine would read the status register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

SEA

MM

TTA

TTR

ECW

TTM

BA

DT

AT

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x0248

Figure 10-7. Arbiter Status Register (XARB_SR)

Table 10-7. XARB_SR Field Descriptions

Bits

Name

Description

31–9

—

Reserved, should be cleared.

8

SEA

Slave Error Acknowledge. This bit is set when an error is detected by any slave devices during the

transfer.

7

MM

Multiple Masters at priority 0. If more than 1 master is recognized at priority 0, this bit is set. Once this

occurs this bit will remain set until cleared. This bit is intended to help in tuning dynamic priority

algorithm development.

6

TTA

TT Address Only. The arbiter automatically AACKs for address only TT codes. This bit is set when this

occurs.

5

TTR

TT Reserved. The arbiter automatically AACKs for reserved TT codes. This bit is set when this occurs.

4

ECW

External Control Word Read/Write. External Control Word Read/Write operations are not supported

on the XL bus. If either occur, the arbiter AACKs and TEAs and sets this bit.

3

TTM

TBST/TSIZ mismatch. Set when an illegal/reserved TBST and TSIZ[0:2] combination occurs. These

combinations are TBST asserted and TSIZ[0:2] = 000, 001, 011, or 1xx (x is 0 or 1).

2

BA

Bus Activity Tenure Time-out. Set when the bus activity time-out counter expires.

1

DT

Data Tenure Time-out. Set when the data tenure time-out counter expires.

0

AT

Address Tenure Time-out. Set when the address tenure time-out counter expires.