3 sdram configuration 1 register settings, Sdram configuration 1 register settings -26, Figure 18-15 – Freescale Semiconductor MCF5480 User Manual

Page 474

MCF548x Reference Manual, Rev. 3

18-26

Freescale Semiconductor

This configuration results in a value of SDRAMDS = 0x0000_0019, as described in

.

18.8.3

SDRAM Configuration 1 Register Settings

The SDCFG1 register should be programmed as shown in

.

This configuration results in a value of SDCFG1 = 0x7362_2830, as described in

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Field

BA

—

Setting

0000_0000_0000_0000

(hex)

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

—

CSSZ

Setting

0000_0000_0001_1001

(hex)

0

0

1

9

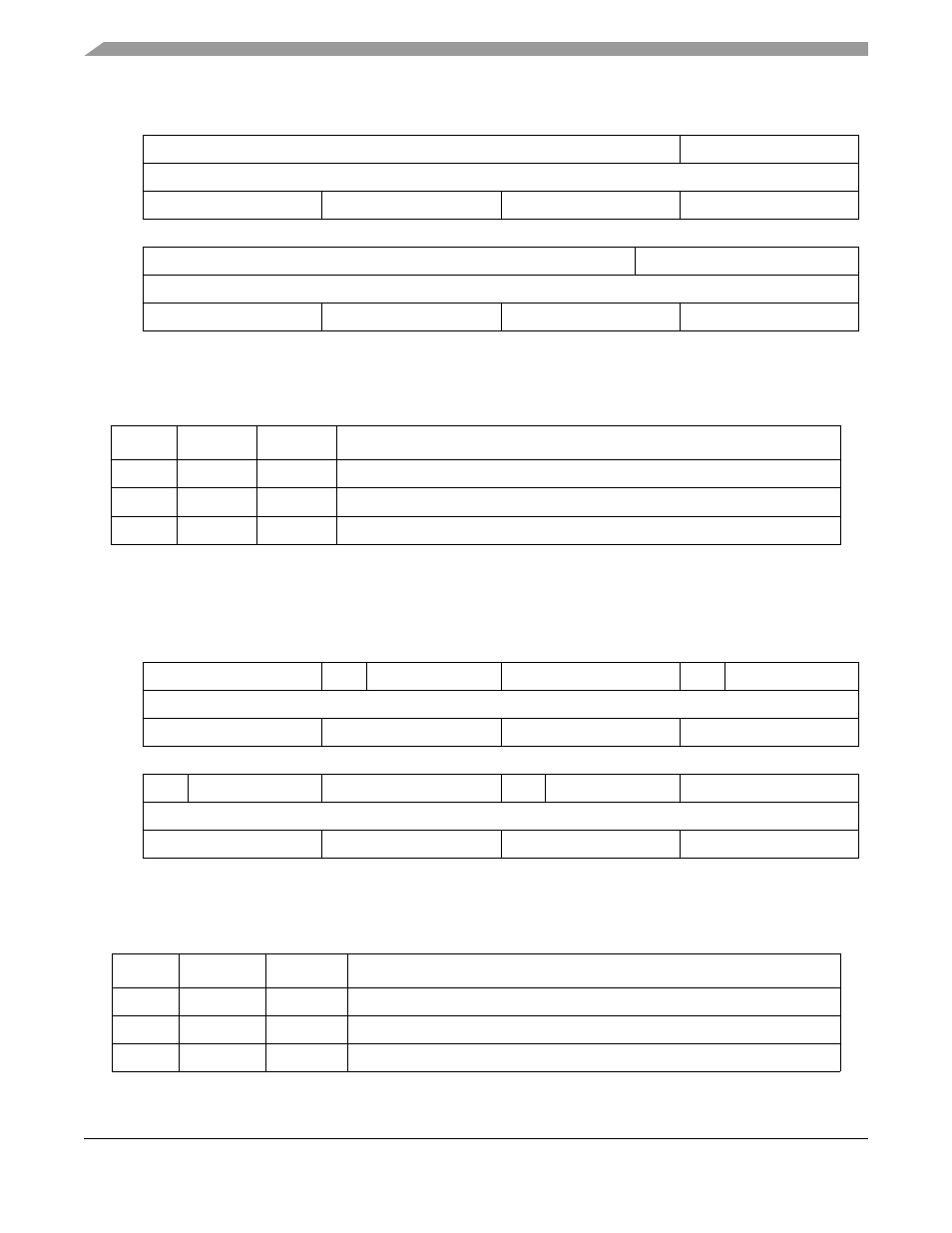

Figure 18-15. SDRAM Example Chip Select 0 Configuration Settings (CS0CFG)

Table 18-16. CS0CFG Field Descriptions

Bits

Name

Setting

Description

31–20

BA

0

Base address is set to 0x0

19–5

—

0

Reserved. Should be cleared.

4–0

CSSZ

1101

Total size is 64 Mbytes. 2 x 256Mbit = 64Mbytes

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Field

SRD2RW

—

SWT2RD

RDLAT

—

ACT2RW

Setting

0111

_0011_0110_0010

(hex)

7

3

6

2

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

—

PRE2ACT

REF2ACT

WTLAT

—

Setting

0010_1000_0011_0000

(hex)

2

8

3

0

Figure 18-16. SDRAM Example Configuration Register 1 Settings (SDCFG1)

Table 18-17. SDCFG1 Field Descriptions

Bits

Name

Setting

Description

31–28

SRD2RW

111

SRD2RW = CASL + (burst length/2) + 1 = 2 + 4+ 1 = 7

27

—

0

Reserved. Should be cleared.

26–24

SWT2RD

011

SWT2RD = t

WR

/SDCLK + 1 = 15ns/8.3ns + 1 = 2.8 clocks, rounded up to 3