Table 8-21 describes xtdr fields – Freescale Semiconductor MCF5480 User Manual

Page 276

MCF548x Reference Manual, Rev. 3

8-26

Freescale Semiconductor

describes XTDR fields.

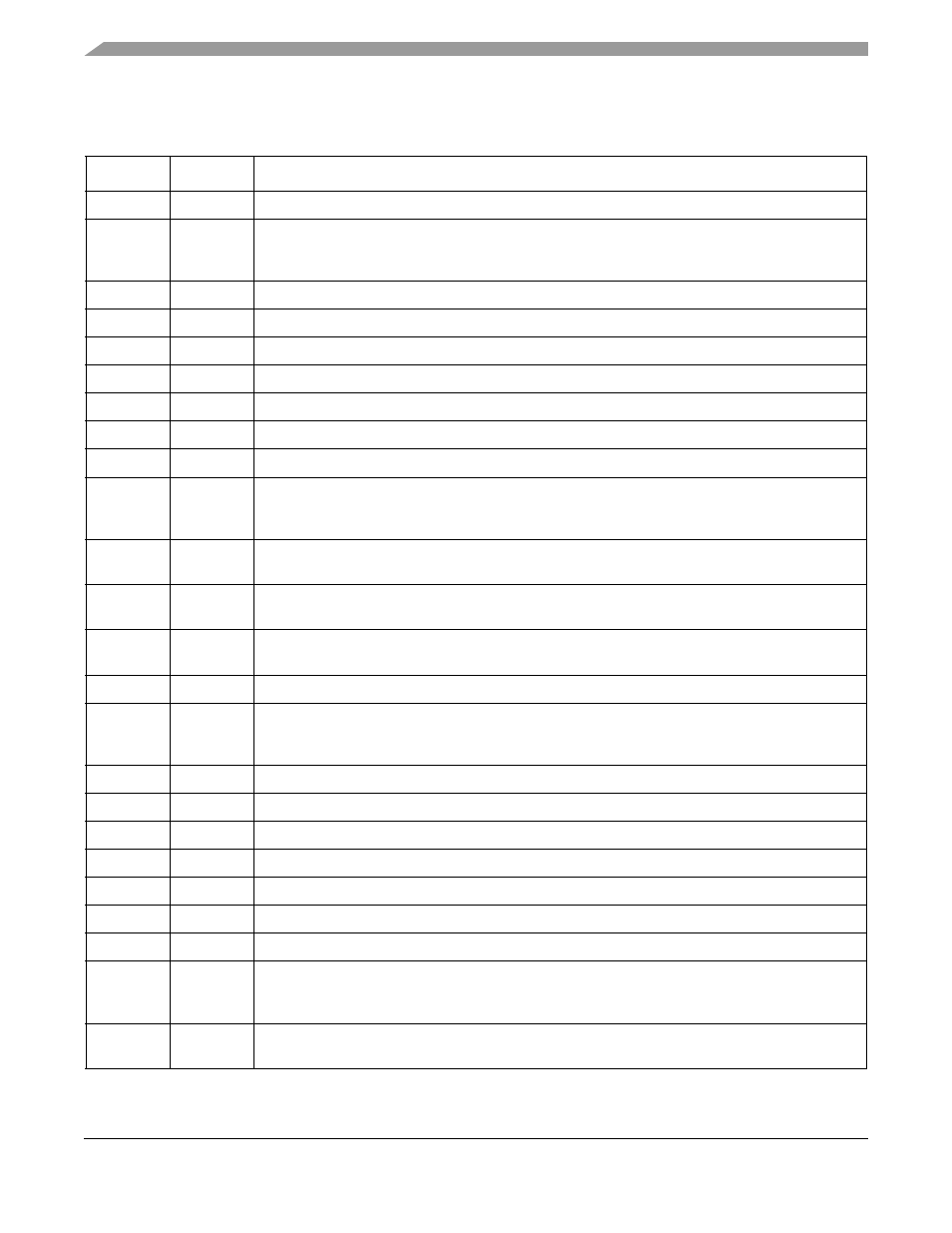

Table 8-21. XTDR Field Descriptions

Bits

Name

Description

31–30

—

Reserved, should be cleared.

29

EBL2

Enable breakpoint level. If set, EBL2 is the global enable for the breakpoint trigger; that is, if

TDR[EBL2] or XTDR[EBL2] is set, a breakpoint trigger is enabled. Clearing both disables all

breakpoints.

28

EDLW2

Data enable bit: Data longword. Entire processor’s local data bus.

27

EDWL2

Data enable bit: Lower data word.

26

EDWU2

Data enable bit: Upper data word.

25

EDLL2

Data enable bit: Lower lower data byte. Low-order byte of the low-order word.

24

EDLM2

Data enable bit: Lower middle data byte. High-order byte of the low-order word.

23

EDUM2

Data enable bit: Upper middle data byte. Low-order byte of the high-order word.

22

EDUU2

Data enable bit: Upper upper data byte. High-order byte of the high-order word.

21

DI2

Data breakpoint invert. Provides a way to invert the logical sense of all the data breakpoint

comparators. This can develop a trigger based on the occurrence of a data value other than the

DBR1 contents.

20

EAI2

Address enable bit: Enable address breakpoint inverted. Breakpoint is based outside the range

between ABLR1 and ABHR1. Trigger if address > ABHR or if address < ABLR.

19

EAR2

Address enable bit: Enable address breakpoint range. The breakpoint is based on the inclusive

range defined by ABLR1 and ABHR1. Trigger if address Š ABHR or if address ð ABLR.

18

EAL2

Address enable bit: Enable address breakpoint low. The breakpoint is based on the address in the

ABLR1. Trigger address = ABLR

17–14

—

Reserved, should be cleared.

13

EBL1

Enable breakpoint level. If set, EBL1 is the global enable for the breakpoint trigger; that is, if

TDR[EBL1] or XTDR[EBL1] is set, a breakpoint trigger is enabled. Clearing both disables all

breakpoints.

12

EDLW1

Data enable bit: Data longword. Entire processor’s local data bus.

11

EDWL1

Data enable bit: Lower data word.

10

EDWU1

Data enable bit: Upper data word.

9

EDLL1

Data enable bit: Lower lower data byte. Low-order byte of the low-order word.

8

EDLM1

Data enable bit: Lower middle data byte. High-order byte of the low-order word.

7

EDUM1

Data enable bit: Upper middle data byte. Low-order byte of the high-order word.

6

EDUU1

Data enable bit: Upper upper data byte. High-order byte of the high-order word.

5

DI1

Data breakpoint invert. Provides a way to invert the logical sense of all the data breakpoint

comparators. This can develop a trigger based on the occurrence of a data value other than the

DBR contents.

4

EAI1

Address enable bit: Enable address breakpoint inverted. Breakpoint is based outside the range

between ABLR1 and ABHR1. Trigger if address > ABHR or if address < ABLR.