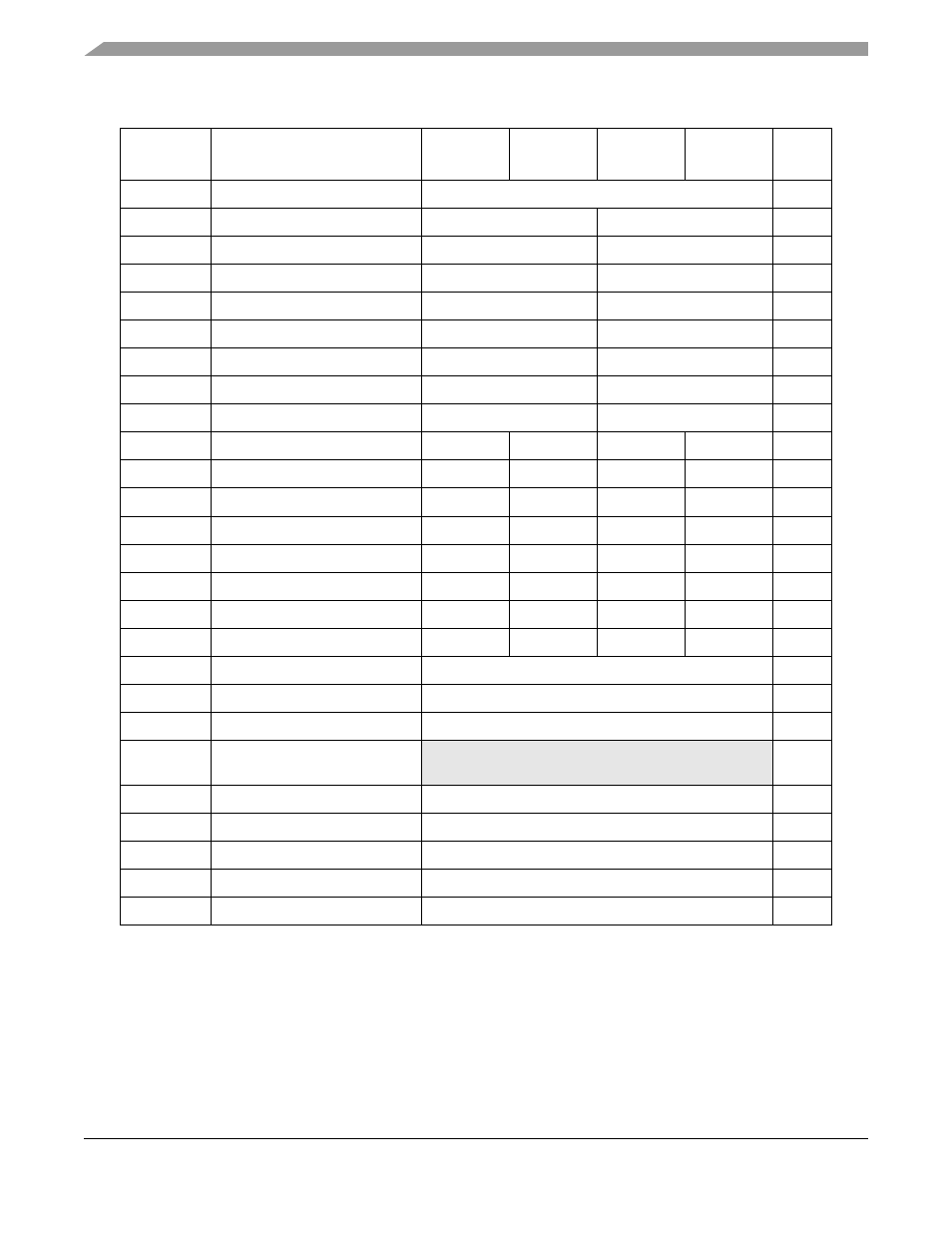

2 task base address register (taskbar), Task base address register (taskbar) -6 – Freescale Semiconductor MCF5480 User Manual

Page 726

MCF548x Reference Manual, Rev. 3

24-6

Freescale Semiconductor

24.3.3.2

Task Base Address Register (TaskBAR)

Note that there is a 512-byte alignment restriction on the TaskBAR.

0x8018

DMA Interrupt Mask Register

DIMR

R/W

0x801C

Task Control Register

TCR0

TCR1

R/W

0x8020

Task Control Register

TCR2

TCR3

R/W

0x8024

Task Control Register

TCR4

TCR5

R/W

0x8028

Task Control Register

TCR6

TCR7

R/W

0x802C

Task Control Register

TCR8

TCR9

R/W

0x8030

Task Control Register

TCR10

TCR11

R/W

0x8034

Task Control Register

TCR12

TCR13

R/W

0x8038

Task Control Register

TCR14

TCR15

R/W

0x803C

Priority Register

PRIOR0

PRIOR1

PRIOR2

PRIOR3

R/W

0x8040

Priority Register

PRIOR4

PRIOR5

PRIOR6

PRIOR7

R/W

0x8044

Priority Register

PRIOR8

PRIOR9

PRIOR10

PRIOR11

R/W

0x8048

Priority Register

PRIOR12

PRIOR13

PRIOR14

PRIOR15

R/W

0x804C

Priority Register

PRIOR16

PRIOR17

PRIOR18

PRIOR19

R/W

0x8050

Priority Register

PRIOR20

PRIOR21

PRIOR22

PRIOR23

R/W

0x8054

Priority Register

PRIOR24

PRIOR25

PRIOR26

PRIOR27

R/W

0x8058

Priority Register

PRIOR28

PRIOR29

PRIOR30

PRIOR31

R/W

0x805C

InitiatorMuxControl IMCR

—

0x8060

Task Size Register 0

TSKSZ0

R/W

0x8064

Task Size Register 1

TSKSZ1

R/W

0x8068 -

0x806f

Reserved

0x8070

Debug Comparator 1

DBGCOMP1

R/W

0x8074

Debug Comparator 2

DBGCOMP2

R/W

0x8078

Debug Control

DBGCTL

R/W

0x807C

Debug Status

DBGSTAT

R/W

0x8080

PTD Debug Registers

PTDDBG

R

1

1

Writes must be to this address first to select the next register to read.

Table 24-1. DMA Memory Map (Continued)

Address

(MBAR +)

Name

Byte0

Byte1

Byte2

Byte3

Access