12 initialization code, Initialization code -34, Precharge sequence and enable write to sdmr – Freescale Semiconductor MCF5480 User Manual

Page 482: Write extended mode register, Write mode register and reset dll, Precharge sequence, Refresh sequence, Write mode register and clear reset dll

MCF548x Reference Manual, Rev. 3

18-34

Freescale Semiconductor

18.8.12 Initialization Code

The following assembly code initializes the DDR SDRAM using the register values determined above.

Basic Configuration and Initialization:

move.l

#0x000002AA, d0//Initialize SDRAMDS

move.l

d0, SDRAMDS

move.l

#0x00000019, d0//Initialize SDCS0

move.l

d0, CS0CFG

move.l

#0x73622830, d0//Initialize SDCFG1

move.l

d0, SDCFG1

move.l

#0x46770000, d0//Initialize SDCFG2

move.l

d0, SDCFG2

Precharge Sequence and enable write to SDMR:

move.l

#0xE10D0002, d0//Initialize SDCR, send PALL, enable SDMR

move.l

d0, SDCR

Write Extended Mode Register:

move.l

#0x40010000, d0//Write LEMR to enable DLL

move.l

d0, SDMR

Write Mode Register and Reset DLL:

move.l

#0x048D0000, d0//Write LMR and reset DLL

move.l

d0, SDMR

Precharge Sequence:

move.l

#0xE10D0002, d0//Send PALL

move.l

d0, SDCR

Refresh Sequence:

move.l

#0xE10D0004, d0//Send first REF command

move.l

d0, SDCR

move.l

#0xE10D0004, d0//Send second REF command

move.l

d0, SDCR

Write Mode Register and Clear Reset DLL:

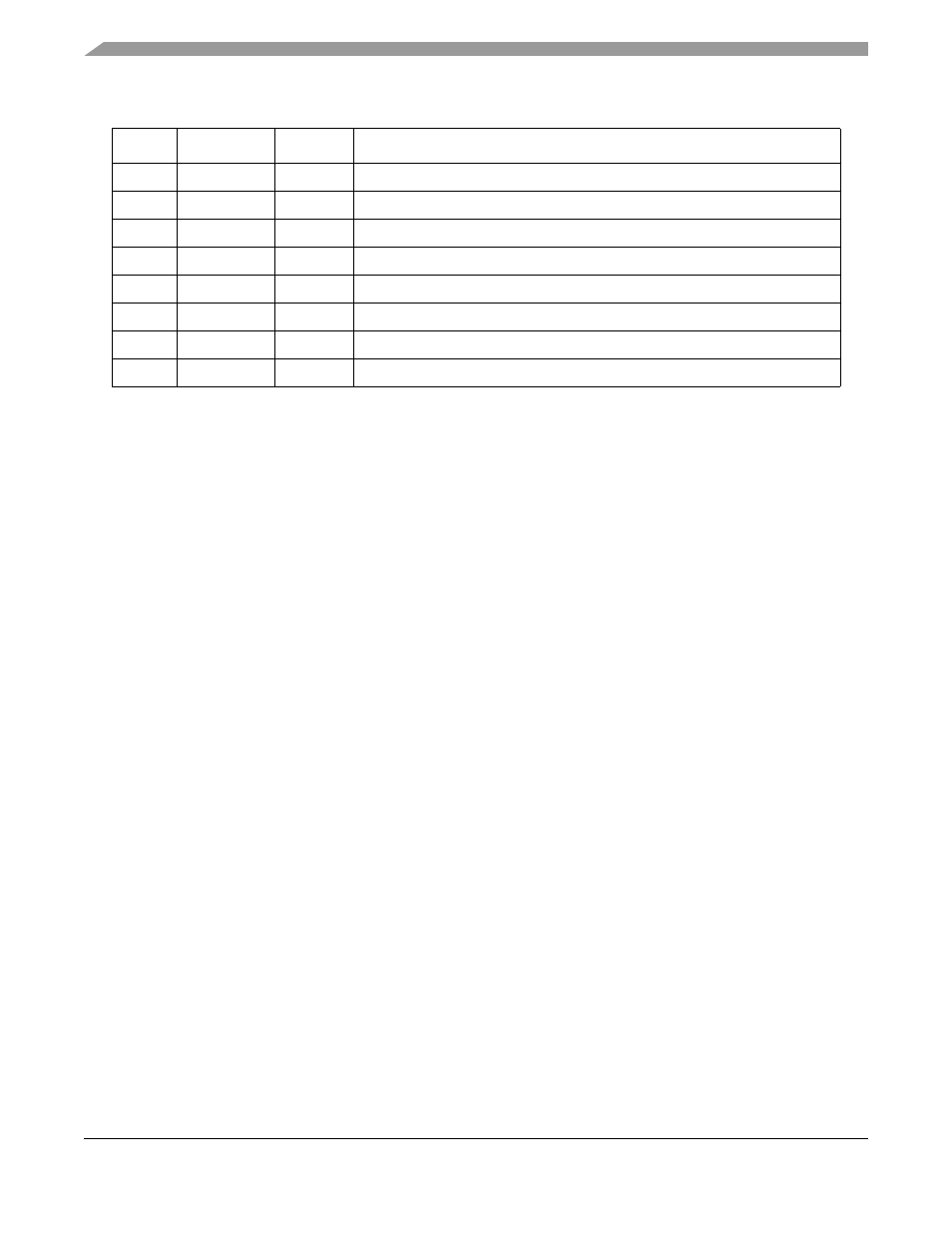

15–12

—

0000

Reserved. Should be cleared.

11–8

DQS_OE

1111

0xF enables drive for all SDDQS pins.

7–5

—

000

Reserved. Should be cleared.

4

BUFF

0

0 indicates that a buffered memory module is not being used.

3

—

0

Reserved. Should be cleared.

2

IREF

0

Initiate a REF command.

1

IPALL

0

Do not initiate a PALL command.

0

—

0

Reserved. Should be cleared.

Table 18-25. SDCR + REF Field Descriptions (Continued)

Bits

Name

Setting

Description