4 mmu operation register (mmuor), Mmu operation register (mmuor) -12, Figure 5-4 – Freescale Semiconductor MCF5480 User Manual

Page 178: Has the address space mode and virtual, Table 5-5 describes mmucr fields, Figure 5-5 shows the mmuor

MCF548x Reference Manual, Rev. 3

5-12

Freescale Semiconductor

5.5.3.4

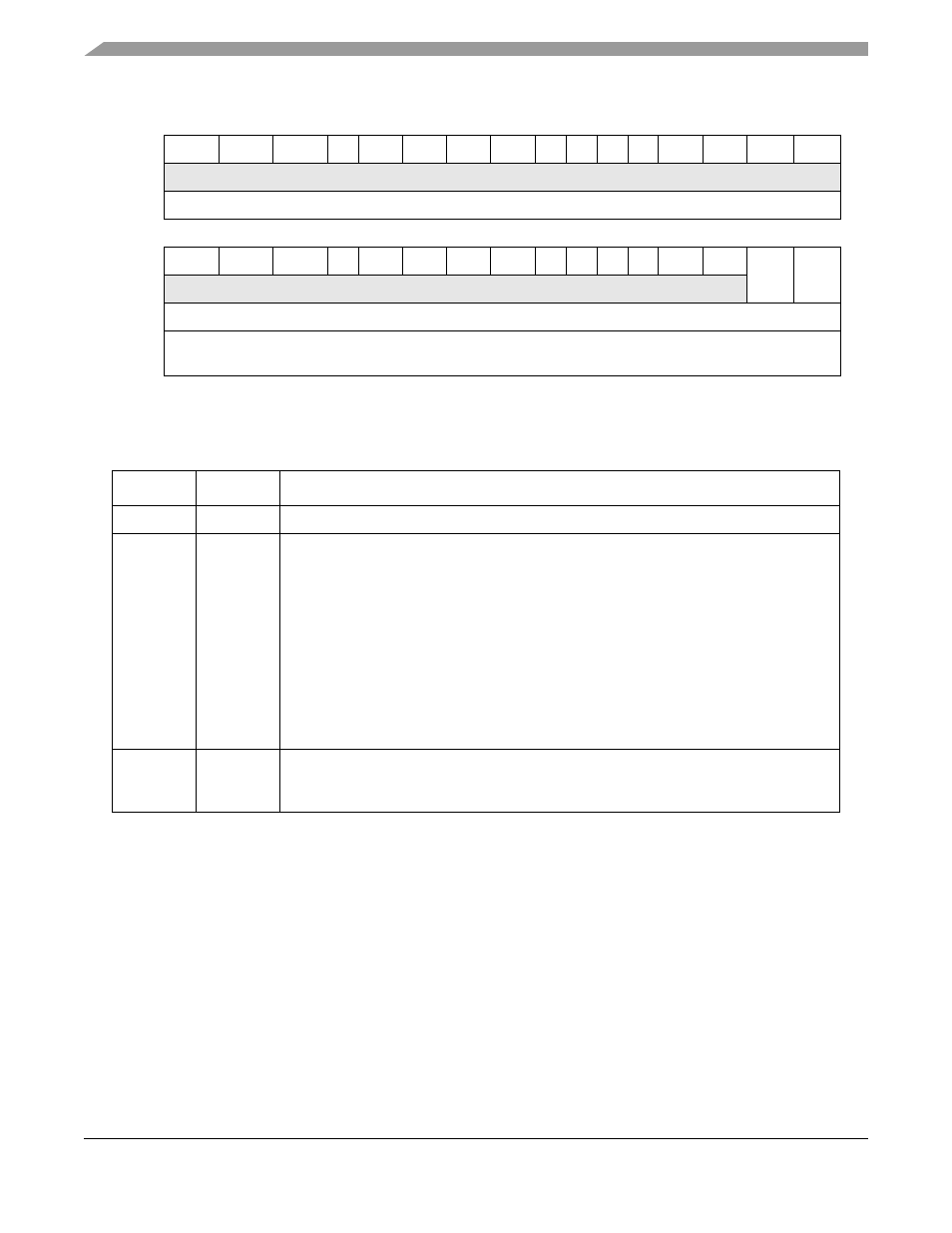

MMU Operation Register (MMUOR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

ASM

EN

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MMUBAR + 0x000

Figure 5-4. MMU Control Register (MMUCR)

Table 5-5. MMUCR Field Descriptions

Bits

Name

Description

31–2

—

Reserved, should be cleared. Writes are ignored and reads return zeros.

1

ASM

Address space mode. Controls how the address space ID is used for TLB hits.

0 TLB entry ASID values are compared to the address space ID register value for user or

supervisor mode unless the TLB entry is marked shared (MMUTR[SG] = 1). The

address space ID register value is the effective address space for all requests,

supervisor and user.

1 Address space 0x00 is reserved for supervisor mode and the effective address space

is forced to 0x00 for all supervisor accesses. The other 255 address spaces are used to

tag user processes. The TLB entry ASID values are compared to the address space ID

register for user mode unless the TLB entry is marked shared (SG = 1). The TLB entry

ASID value is always compared to 0x00 for supervisor accesses. This allows two levels

of sharing. All users but not the supervisor share an entry if SG = 1and ASID ¦ 0. All

users and the supervisor share an entry if SG = 1 and ASID = 0

0

EN

Virtual mode enabled. Indicates when virtual mode is enabled.

0 Virtual mode is disabled.

1 Virtual mode is enabled.