3 functional description, Functional description -8 – Freescale Semiconductor MCF5480 User Manual

Page 416

MCF548x Reference Manual, Rev. 3

16-8

Freescale Semiconductor

16.3

Functional Description

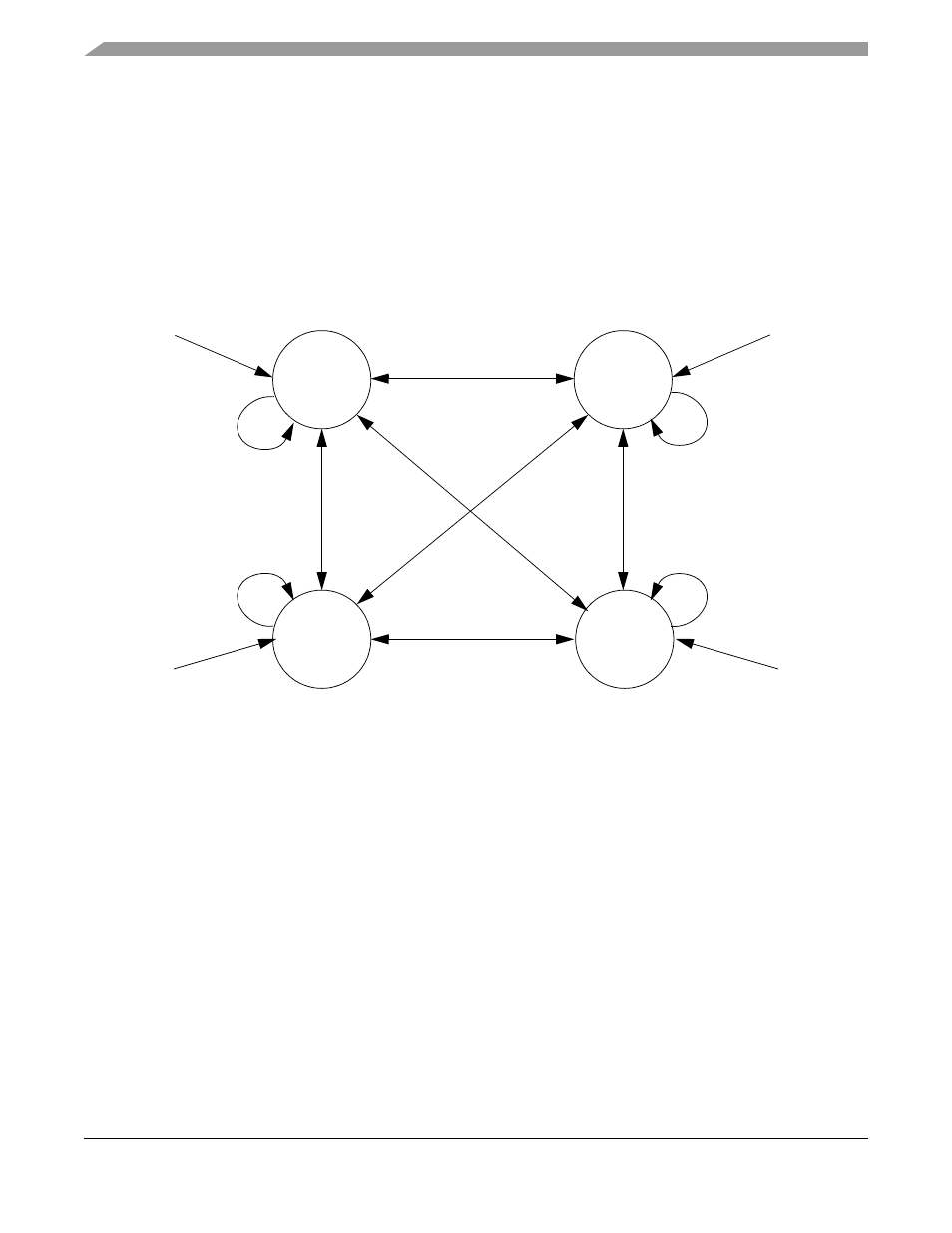

The system SRAM decodes the addresses for all four banks to determine which master is trying to access

which bank. The system SRAM module provides a bus arbitration mechanism for granting access of each

bank to each master. All masters simply request a data transfer and the SRAM grants a specified cycle

count to the appropriate master. The arbitration is overlapped with the address phase of SRAM transfers

and therefore imposes no performance penalty or overhead.

The current master pointer for each bank is determined as shown in

. The current master

pointer transitions to another master when the current master’s maximum transfer count is exceeded, or

the current master is idle and another master requests access to the bank. Otherwise, the current master

pointer remains unchanged.

Figure 16-7. SRAM Arbitration

Master

SEC

DMA-R

RE

SET

(Ban

k 0)

RES

ET

(Ba

nk 1

)

RESET

(Bank

2)

RE

SE

T

(Ba

nk

3)

DMA-W