6 dspi tx fifo register (dtfr), Dspi tx fifo register (dtfr) -15 – Freescale Semiconductor MCF5480 User Manual

Page 833

Memory Map and Registers

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

27-15

27.6.6

DSPI Tx FIFO Register (DTFR)

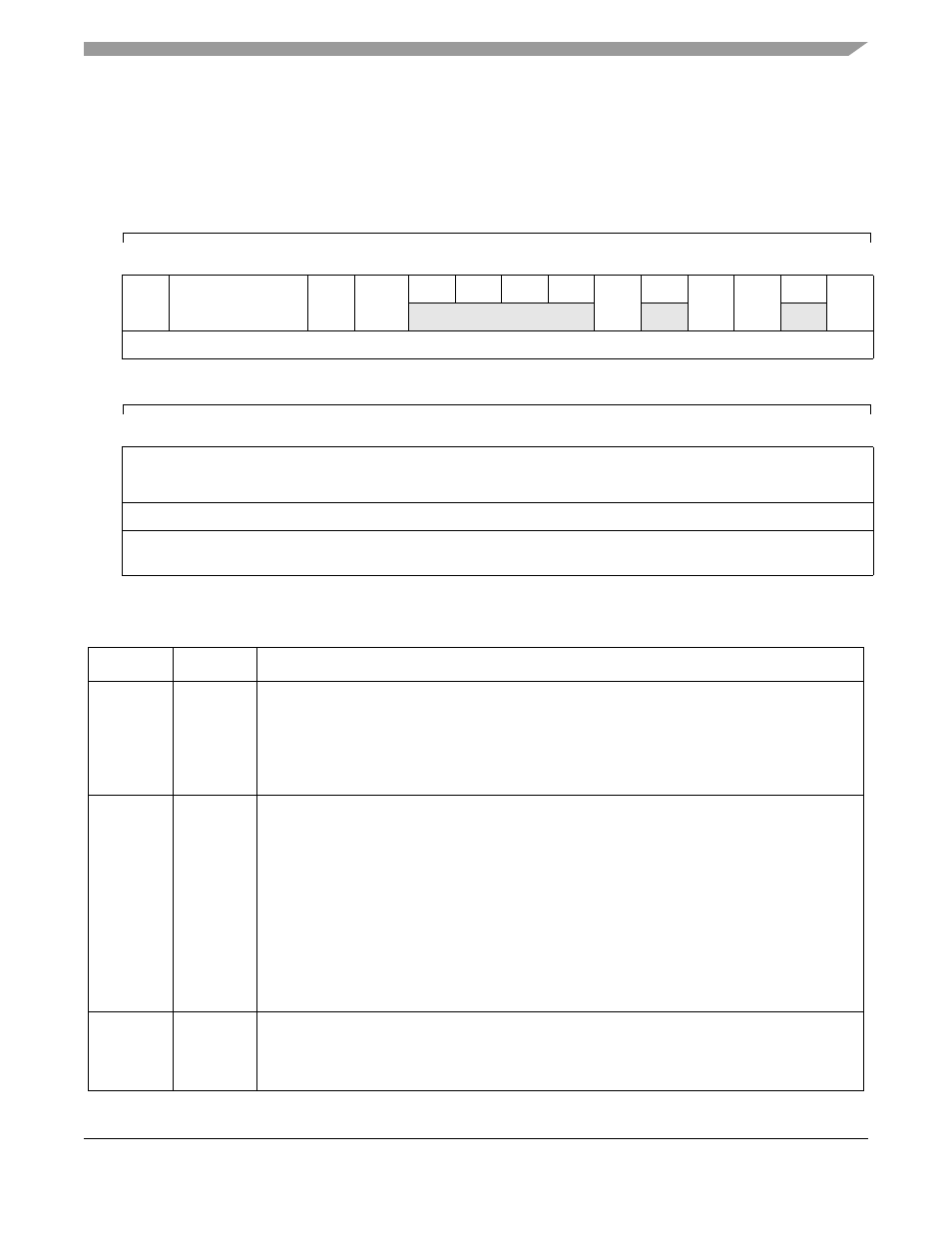

The DTFR provides a means to write to the Tx FIFO. SPI commands and data written to this register are

transferred to the Tx FIFO. See

Section 27.7.2.4, “Tx FIFO Buffering Mechanism

” for more information.

8- or 16-bit write accesses to the DTFR will transfer 32 bits to the Tx FIFO.

SPI Command Field

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R CONT

CTAS

EOQ CTCNT

0

0

0

0

CS5

0

CS3

CS2

0

CS0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SPI Data Field

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

TXDATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8A34

Figure 27-7. DSPI Tx FIFO Register (DTFR)

Table 27-10. DTFR Field Descriptions

Bits

Name

Description

31

CONT

Continuous peripheral chip select enable. The CONT bit selects a continuous selection format.

The bit is used in SPI master mode. The bit enables the selected

DSPICSn signals to remain

asserted between transfers. See

Section 27.7.4.5, “Continuous Selection Format

' for more

information.

0 DSPICSn signals return to their inactive state between transfers

1 DSPICSn signals stay asserted between transfers

30–28

CTAS

Clock and transfer attributes select. The CTAS field selects which of the DCTAR registers is used

to set the transfer attributes for the associated SPI frame. The field is only used in SPI master

mode. In SPI slave mode DCTAR0 is used. The number of DSPI_CTAR registers is

implementation specific.

000 DCTAR0 determines clock and attributes for transfer

001 DCTAR1 determines clock and attributes for transfer

010 DCTAR2 determines clock and attributes for transfer

011 DCTAR3 determines clock and attributes for transfer

100 DCTAR4 determines clock and attributes for transfer

101 DCTAR5 determines clock and attributes for transfer

110 DCTAR6 determines clock and attributes for transfer

111 DCTAR7 determines clock and attributes for transfer

27

EOQ

End of queue. The EOQ bit provides a means for host software to signal to the DSPI that the

current SPI transfer is the last in a queue. At the end of the transfer the EOQF bit in the DSR is set.

0 The SPI data is not the last data to transfer

1 The SPI data is the last data to transfer