Figure 7-4, D). this process is described – Freescale Semiconductor MCF5480 User Manual

Page 229

Cache Organization

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

7-9

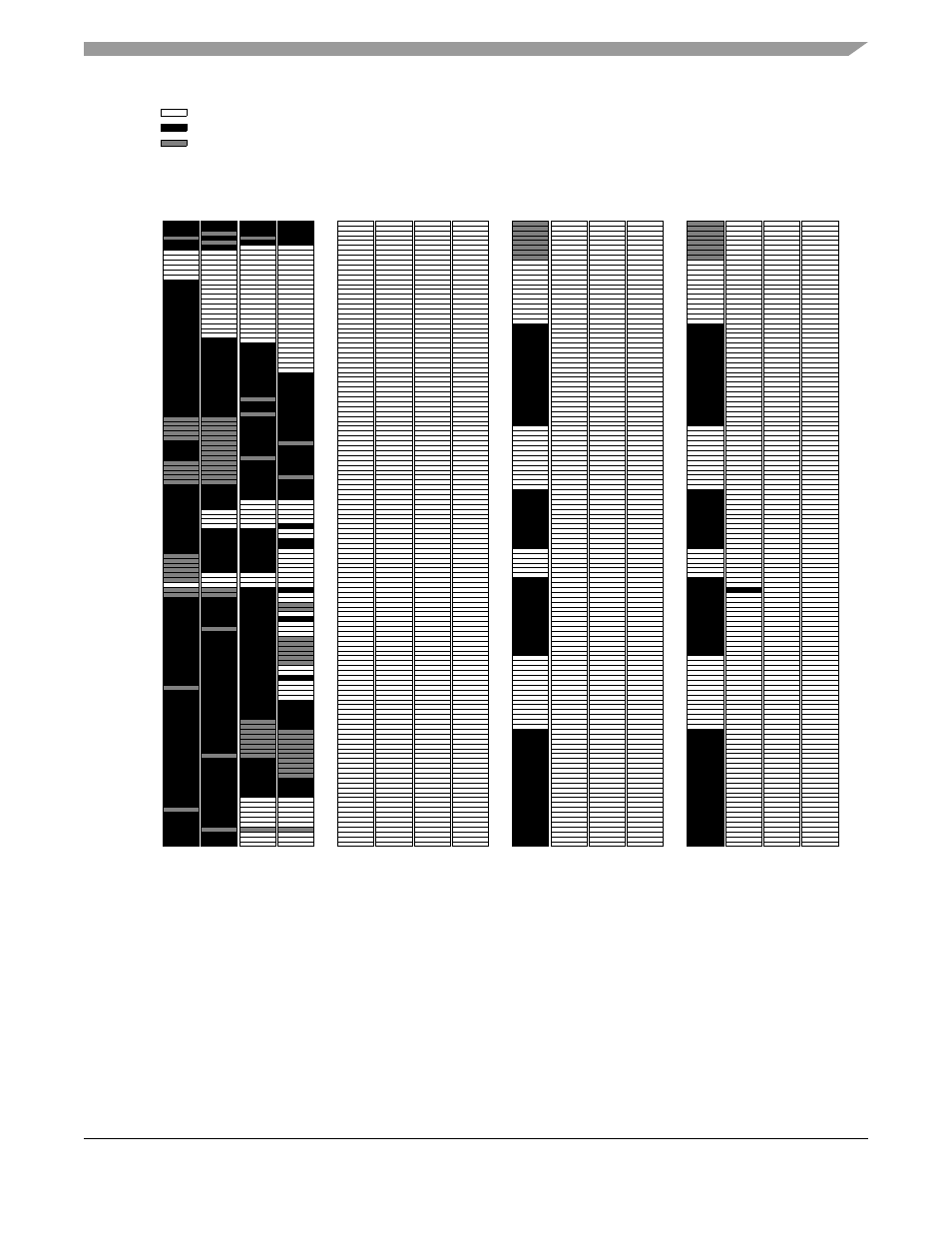

Figure 7-4. Data Cache—A: at Reset, B: after Invalidation, C and D: Loading Pattern

A: Cache population at

start-up

B: Cache after invalidation,

before it is enabled

C: Cache after loads in

Way 0

D: First load in Way 1

Way 0Way 1Way 2Way 3

Way 0Way 1Way 2Way 3

Way 0Way 1Way 2Way 3

Way 0Way 1Way 2Way 3

Invalid (V = 0)

Valid, not modified (V = 1, M = 0)

Valid, modified (V = 1, M = 1)

At reset, cache contents

are indeterminate; V and

M may be set. The cache

should be cleared

explicitly by setting

CACR[DCINVA] before

the cache is enabled.

Setting CACR[DCINVA]

invalidates the entire

cache.

Set 0

Set 511

Initial cacheable

accesses to memory-fill

positions in way 0.

A line is loaded in way 1

only if that set is full in

way 0.