5 fbcs register (podr_fbcs), 2 port x data direction registers (pddr_x), Port – Freescale Semiconductor MCF5480 User Manual

Page 383: Figure 15-5, Figure 15-6, 2 port x data direction registers (pddr_ x )

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

15-11

15.3.2.1.5

FBCS Register (PODR_FBCS)

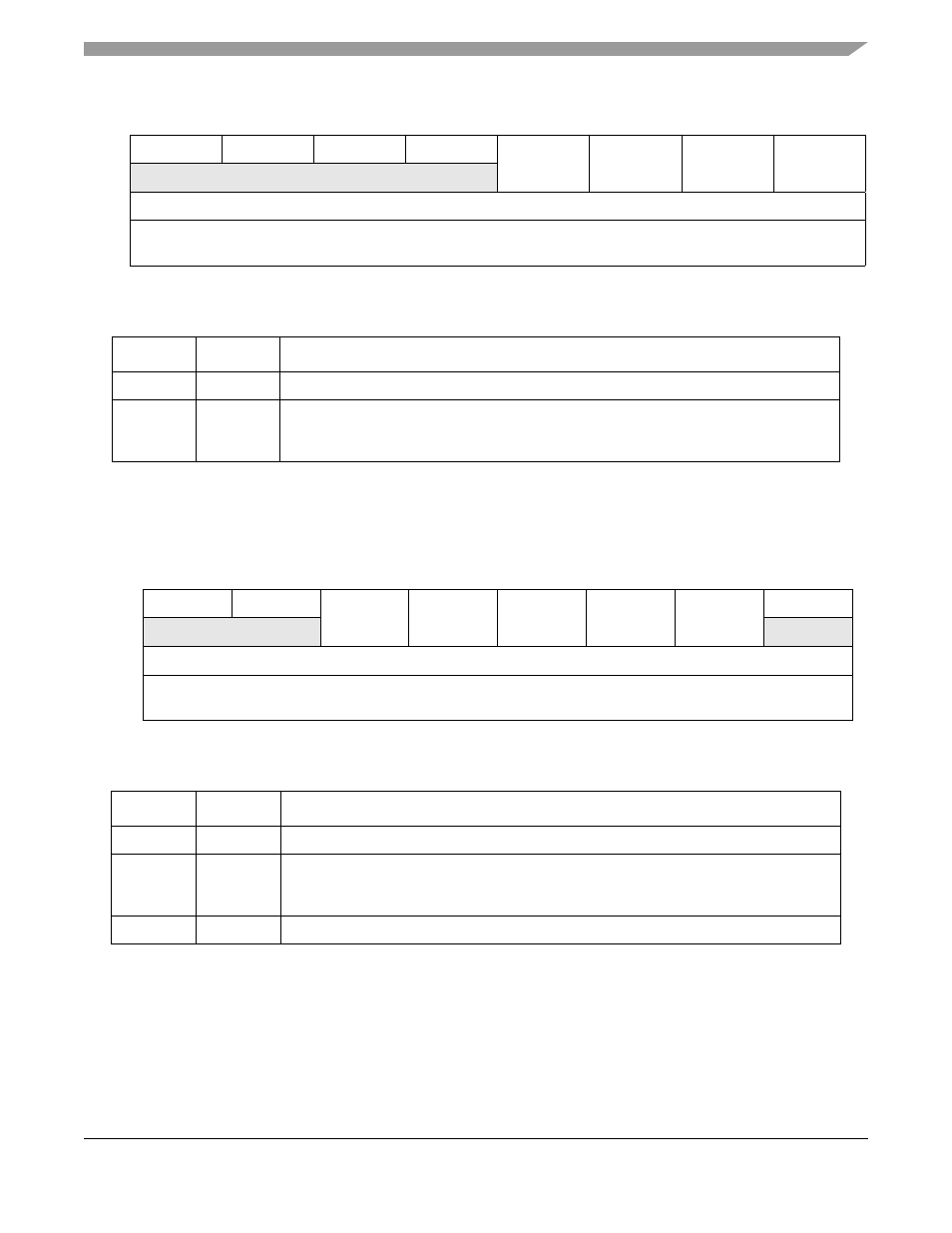

The 5-bit PODR_FBCS register is the output data register for PFBCSn (PODR_FBCS).

displays the 5-bit PODR_FBCS register.

15.3.2.2

Port x Data Direction Registers (PDDR_x)

The PDDR registers control the direction of the port x pin drivers when the pins are configured for general

purpose I/O.

7

6

5

4

3

2

1

0

R

0

0

0

0

PODRx3

PODRx2

PODRx1

PODRx0

W

Reset

0

0

0

0

1

1

1

1

Reg

Addr

MBAR + 0xA02 (PORT_DMA), 0xA08 (PORT_FECI2C)

Figure 15-5. 4-Bit PODR_DMA and PODR_FECI2C Registers

Table 15-7. 4-Bit PODR_DMA and PODR_FECI2C Field Descriptions

Bits

Name Description

7–4

—

Reserved, should be cleared

3–0

PODRxn

PORT_DMA and PORT_FECI2C output data bits

0 Drive 0 when PDMAn or PFECI2Cn pin is general purpose output

1 Drive 1 when PDMAn or PFECI2Cn pin is general purpose output

7

6

5

4

3

2

1

0

R

0

0

PODRFB5

PODRFB4

PODRFB3

PODRFB2

PODRFB1

0

W

Reset

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xA01 (PODR_FBCS)

Figure 15-6. 5-Bit PODR_FBCS Register

Table 15-8. 5-Bit PODR_FBCS Field Descriptions

Bits

Name Description

7–6

—

Reserved, should be cleared

5–1

PODRFBn

PORT_FBCS output data

0 Drive 0 when PFBCSn pin is general purpose output

1 Drive 1 when PFBCSn pin is general purpose output

0

—

Reserved, should be cleared