Psctfarn), The fifo (see – Freescale Semiconductor MCF5480 User Manual

Page 794

MCF548x Reference Manual, Rev. 3

26-32

Freescale Semiconductor

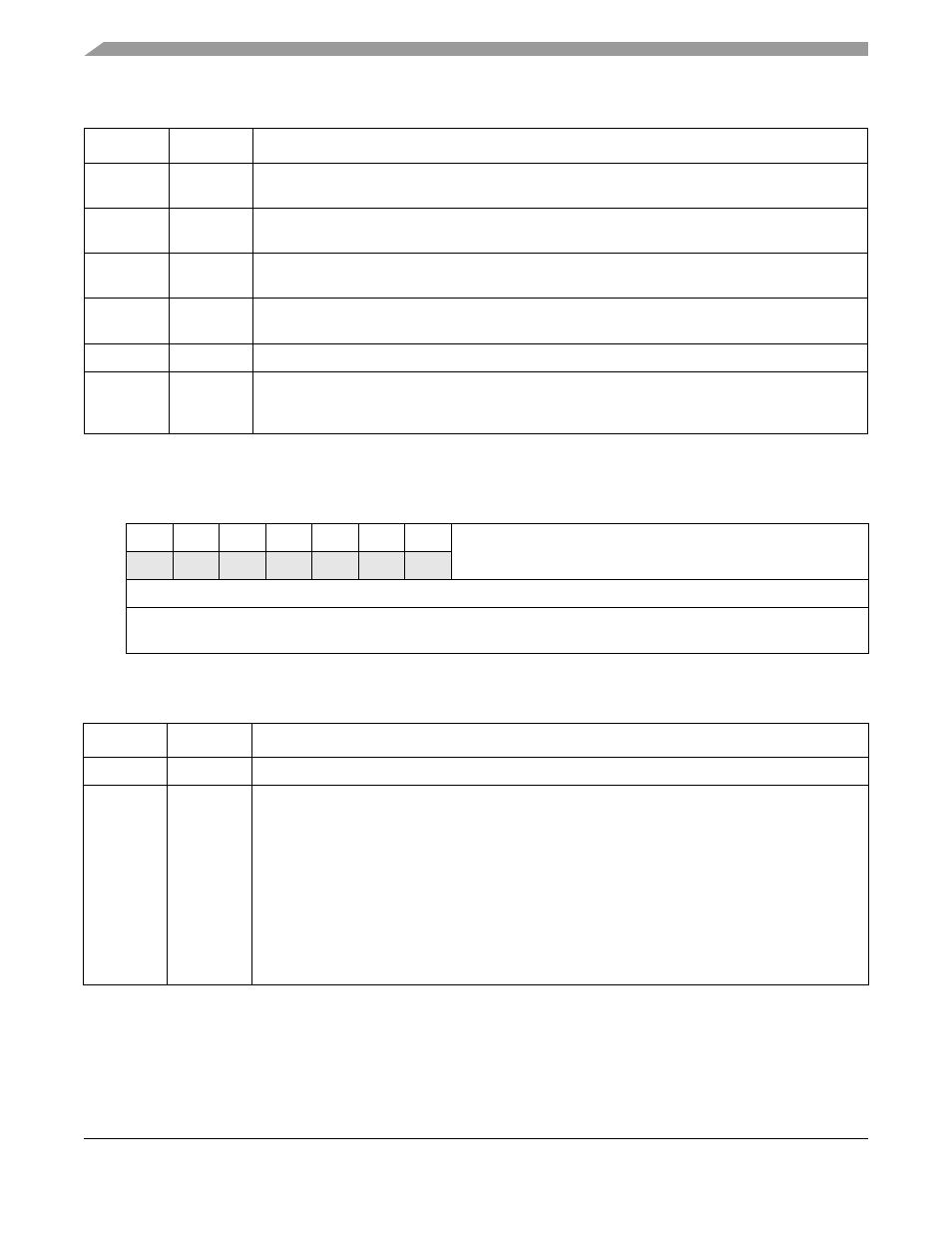

26.3.3.25 Rx and Tx FIFO Alarm Register (PSCRFARn, PSCTFARn)

26.3.3.26 Rx and Tx FIFO Read Pointer (PSCRFRPn, PSCTFRPn)

The read pointer is a FIFO-maintained pointer that points to the next FIFO location to be read. The physical

address of this FIFO location is actually the combination of the read pointer and the FIFO base, which is

21

RXW_MSK Receive wait condition mask. When this bit is set, the FIFO controller masks the status register’s

RXW bit from generating an error.

20

UF_MSK

FIFO underflow mask. When this bit is set, the FIFO controller masks the status register’s UF bit

from generating an error.

19

OF_MSK

FIFO overflow mask. When this bit is set, the FIFO controller masks the status register’s OF bit from

generating an error.

18

TXW_MSK Transmit wait condition mask. When this bit is set, the FIFO controller masks the status register’s

TXW bit from generating an error.

17-16

—

Reserved, should be cleared.

15-0

CNTR

Timer mode counter. When the TMR bit is set, the value of the COUNTER[15:0] bits are used to

determine the period of time that the frame ready request is suppressed. A request for service will

be made every (COUNTER[15:0] * 64) cycles as long as a valid frame exists in the FIFO.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

ALARM

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x866E (PSCRFAR0); 0x876E (PSCRFAR1); 0x886E (PSCRFAR2); 0x896E (PSCRFAR3)

and MBAR + 0x868E (PSCTFAR0); 0x878E (PSCTFAR1); 0x888E (PSCTFAR2); 0x898E (PSCTFAR3)

Figure 26-22. RxFIFO (PSCRFARn) and TxFIFO (PSCTFARn) Alarm Register

Table 26-32. PSCRFARn and PSCTFARn Field Descriptions

Bits

Name

Description

15–9

—

Reserved, should be cleared.

8–0

ALARM

Alarm pointer

For Transmitter: The user writes these bits to set the low level “watermark”, which is the point at

which the FIFO asserts its request for data filling to the DMA controller. This value is in bytes. For

example, with ALARM = 32, the alarm condition will occur when the FIFO has 32 (or less) bytes in

it. The alarm, once asserted, will not negate until the high level mark is reached, as specified by the

granularity bits in the PSCTFCR.

For Receiver: The user writes these bits to set the high level “watermark”, which is the point at which

the FIFO asserts its request for data emptying to the DMA controller. This value is in bytes. For

example, with ALARM = 32, the alarm condition will occur when the FIFO has 32 (or more) bytes in

it. The alarm, once asserted will not negate until the low level mark is reached, as specified by the

granularity bits in the PSCRFCR.

Table 26-31. PSCRFCRn and PSCRTFCRn Field Descriptions (Continued)

Bits

Name

Description