Freescale Semiconductor MCF5480 User Manual

Page 260

MCF548x Reference Manual, Rev. 3

8-10

Freescale Semiconductor

are accessed through the BDM port by BDM commands,

WDMREG

and

RDMREG

,

described in

Section 8.5.3.3, “Command Set Descriptions

.” These commands contain a 5-bit field, DRc,

that specifies the register, as shown in

These registers are also accessible from the processor’s supervisor programming model through the

execution of the WDEBUG instruction. Thus, the external development system and the operating system

running on the processor core can access the breakpoint hardware. It is the responsibility of the software

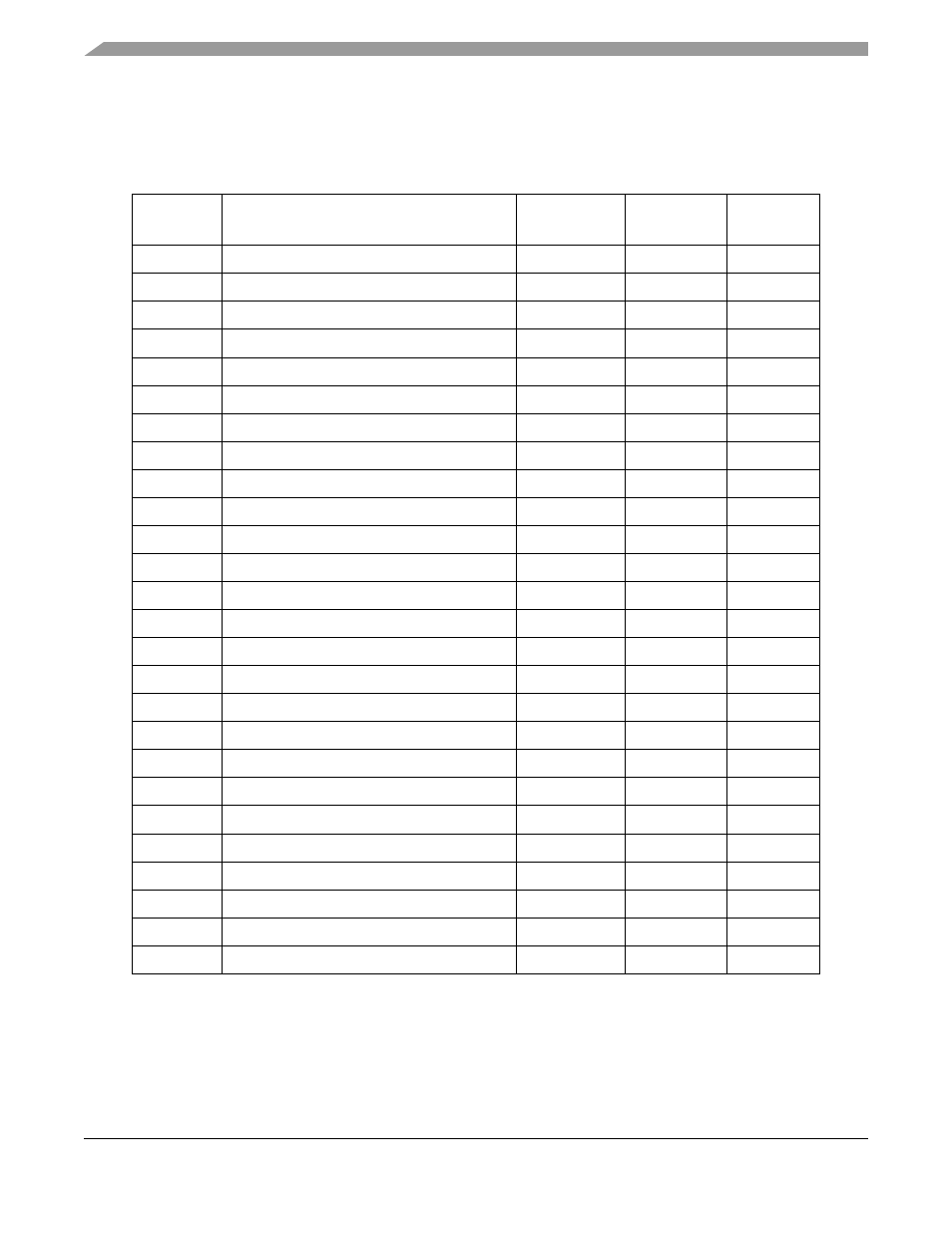

Table 8-6. BDM/Breakpoint Registers

DRc[4–0]

Register Name

Abbreviation

Initial State

Section/

Page

0x00

Configuration/status register

1

1

CSR is write-only from the programming model. It can be read or written through the BDM port using the

RDMREG and WDMREG commands.

CSR

0x0020_0000

0x01–0x05

Reserved

—

—

—

0x04

PC breakpoint ASID control

PBAC

—

0x05

BDM address attribute register

BAAR

0x0000_0005

0x06

Address attribute trigger register

AATR

0x0000_0005

0x07

Trigger definition register

TDR

0x0000_0000

0x08

Program counter breakpoint register

PBR

—

0x09

Program counter breakpoint mask register

PBMR

—

0x0A–0x0B

Reserved

—

—

—

0x0C

Address breakpoint high register

ABHR

—

0x0D

Address breakpoint low register

ABLR

—

0x0E

Data breakpoint register

DBR

—

0x0F

Data breakpoint mask register

DBMR

—

0x10–0x153 Reserved

—

—

—

0x14

PC breakpoint ASID register

PBASID

—

0x15

Reserved

—

—

—

0x16

Address attribute trigger register 1

AATR1

0x0000_0005

0x17

Extended trigger definition register

XTDR

0x0000_0000

0x18

Program counter breakpoint 1 register

PBR1

0x0000_0000

0x19

Reserved

—

—

—

0x1A

Program counter breakpoint register 2

PBR2

0x0000_0000

0x1B

Program counter breakpoint register 3

PBR3

0x0000_0000

0x1C

Address high breakpoint register 1

ABHR1

—

0x1D

Address low breakpoint register 1

ABLR1

—

0x1E

Data breakpoint register 1

DBR1

—

0x1F

Data breakpoint mask register 1

DBMR1

—