6 mib control register (mibc), 7 receive control register (rcr), Mib control register (mibc) -17 – Freescale Semiconductor MCF5480 User Manual

Page 947: Receive control register (rcr) -17

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

30-17

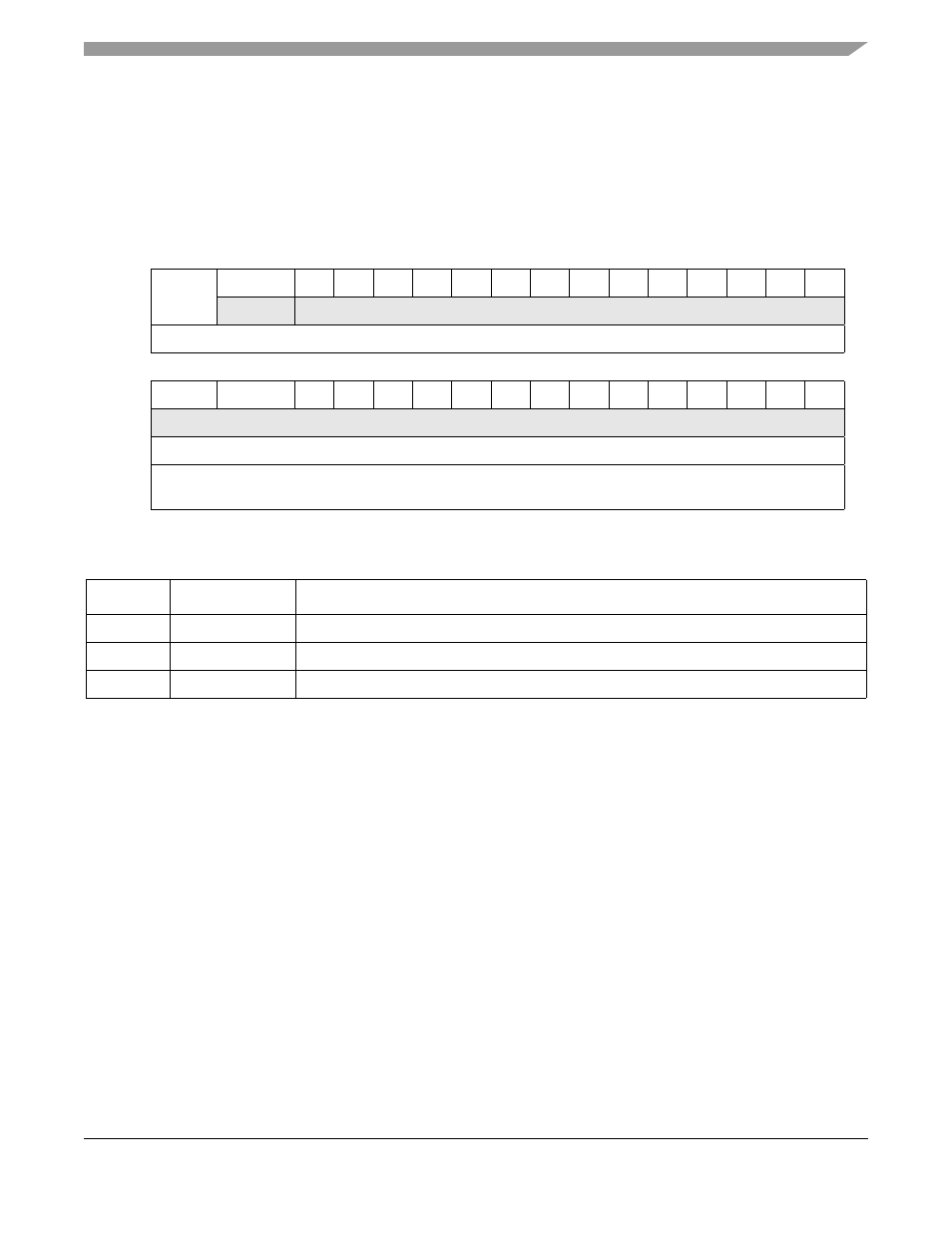

30.3.3.6

MIB Control Register (MIBC)

The MIBC is a read/write register used to provide control of and to observe the state of the MIB block.

This register is accessed by user software if there is a need to disable the MIB block operation. For

example, in order to clear all MIB counters in RAM the user should disable the MIB block, then clear all

the MIB RAM locations, then enable the MIB block. The MIB_DISABLE bit is reset to 1. See

for the locations of the MIB counters.

30.3.3.7

Receive Control Register (RCR)

The RCR is programmed by the user. The RCR controls the operational mode of the receive block and

should be written only when ECR[ETHER_EN] = 0 (initialization time).

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

MIB_

DISABLE

MIB_IDLE

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x9064 (FEC0), 0x9864 (FEC1)

Figure 30-7. MIB Control Register (MIBC)

Table 30-13. MIBC Field Descriptions

Bits

Name

Description

31

MIB_DISABLE

A read/write control bit. If set, the MIB logic will halt and not update any MIB counters.

30

MIB_IDLE

A read-only status bit. If set, the MIB block is not currently updating any MIB counters.

29–0

—

Reserved, should be cleared.