Freescale Semiconductor MCF5480 User Manual

Page 830

MCF548x Reference Manual, Rev. 3

27-12

Freescale Semiconductor

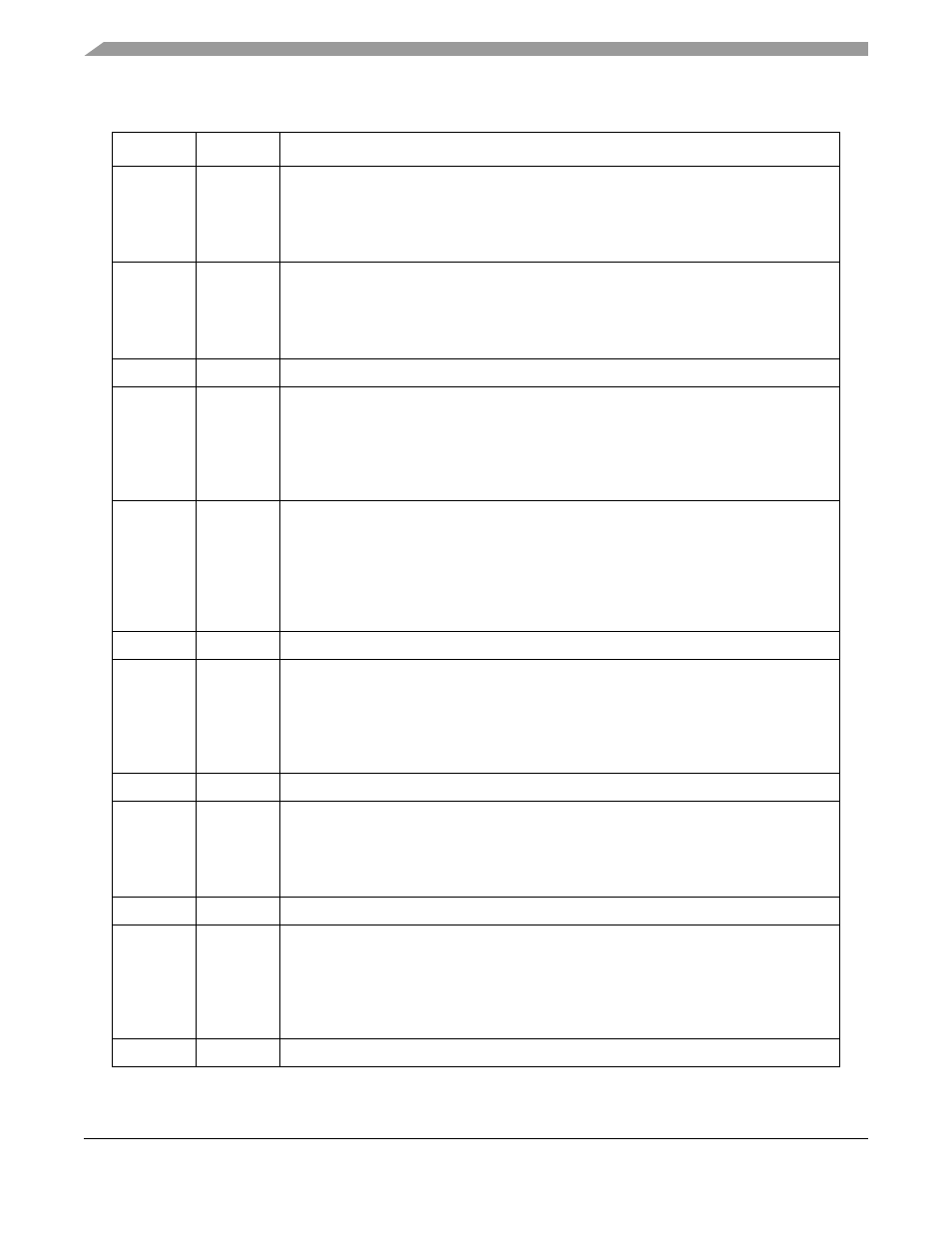

Table 27-9. DSR Field Descriptions

Bits

Name

Description

31

TCF

Transfer complete flag. The TCF bit indicates that all bits in a frame have been shifted out.

The TCF bit is set at the end of the frame transfer. The TCF bit remains set until cleared

by software.

0 Transfer not complete

1 Transfer complete

30

TXRXS

Transmit and receive status. The TXRXS bit reflects the status of the DSPI. See

Section 27.7.1, “Start and Stop of DSPI Transfers

” for information on how what causes this

bit to be negated or asserted.

0 Transmit and receive operations are disabled (DSPI is in Stopped state)

1 Transmit and receive operations are enabled (DSPI is in Running state)

29

—

Reserved, should be cleared.

28

EOQF

End of queue flag. The EOQF bit indicates that transmission in progress is the last entry

in a queue. The EOQF bit is set when Tx FIFO entry has the EOQ bit set in the command

halfword and the end of the transfer is reached. The EOQF bit remains set until cleared by

software. When the EOQF bit is set, the TXRXS bit is automatically cleared.

0 EOQ is not set in the executing command

1 EOQ is set in the executing SPI command

27

TFUF

Transmit FIFO underflow flag. The TFUF bit indicates that an underflow condition in the Tx

FIFO has occurred. The transmit underflow condition is detected only for DSPI blocks

operating in slave mode. The TFUF bit is set when the Tx FIFO of a DSPI operating in slave

mode is empty, and a transfer is initiated by an external SPI master. The TFUF bit remains

set until cleared by software.

0 Tx FIFO underflow has not occurred

1 Tx FIFO underflow has occurred

26

—

Reserved, should be cleared.

25

TFFF

Transmit FIFO fill flag. The TFFF bit provides a method for the DSPI to request more

entries to be added to the Tx FIFO. The TFFF bit is set while the Tx FIFO is not full. The

TFFF bit can be cleared by host software or an acknowledgement from the DMA controller

when the Tx FIFO is full.

0 Tx FIFO is full

1 Tx FIFO is not full

24–20

—

Reserved, should be cleared.

19

RFOF

Receive FIFO overflow flag. The RFOF bit indicates that an overflow condition in the Rx

FIFO has occurred. The bit is set when the Rx FIFO and shift register are full and a transfer

is initiated. The bit remains set until cleared by software.

0 Rx FIFO overflow has not occurred

1 Rx FIFO overflow has occurred

18

—

Reserved, should be cleared

17

RFDF

Receive FIFO drain flag. The RFDF bit provides a method for the DSPI to request that

entries be removed from the Rx FIFO. The bit is set while the Rx FIFO is not empty. The

RFDF bit can be cleared by host software or an acknowledgement from the DMA controller

when the Rx FIFO is empty.

0 Rx FIFO is empty

1 Rx FIFO is not empty

16

—

Reserved, should be cleared.