Table iv. mcf548 x revision history (continued) – Freescale Semiconductor MCF5480 User Manual

Page 52

MCF548x Reference Manual, Rev. 3

lii

Freescale Semiconductor

Insert the following section before section 10.2 “XL Bus Arbiter”.

10.2 PLL

10.2.1 PLL Memory Map/Register Descriptions

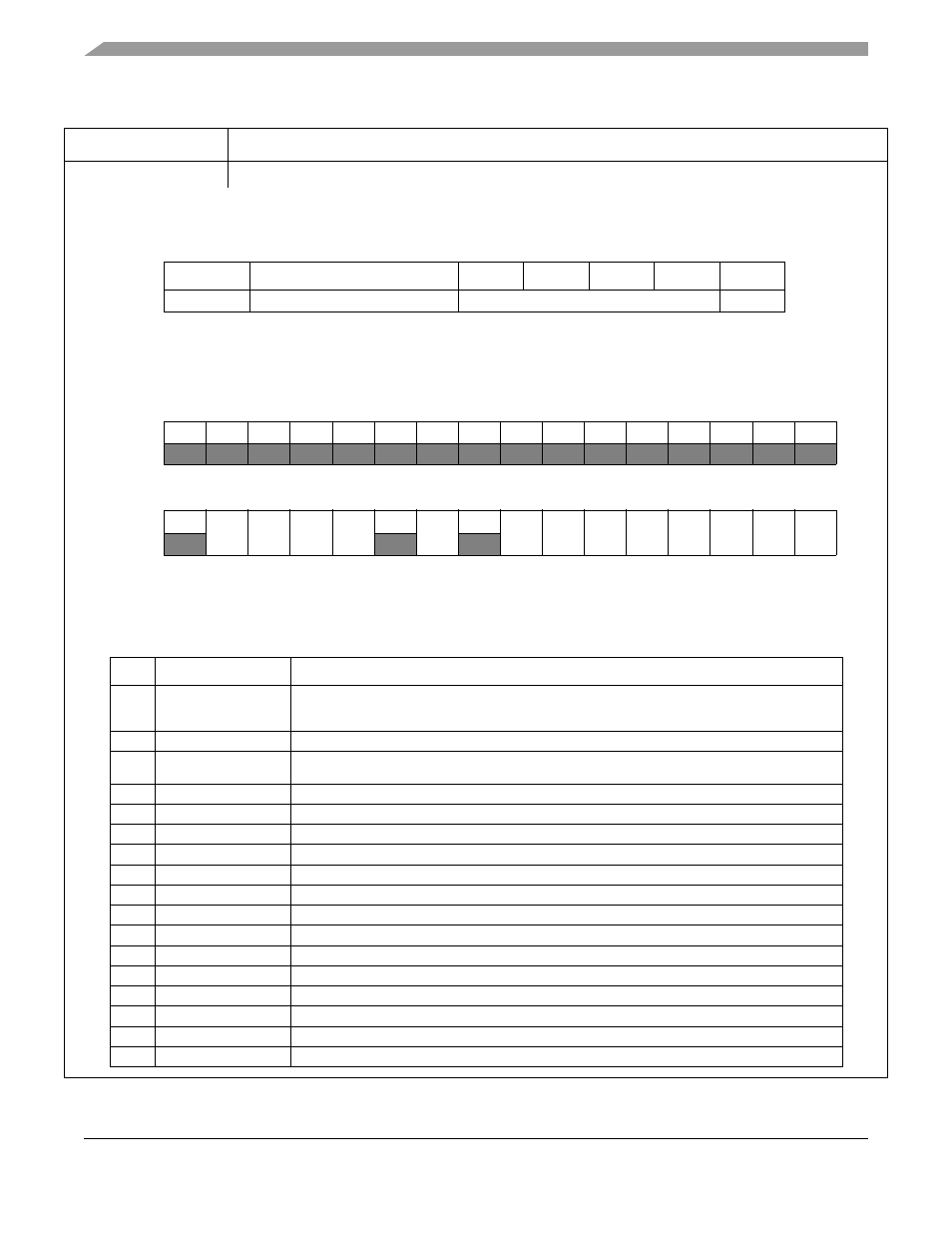

10.2.2 System PLL Control Register (SPCR)

The system PLL control register (SPCR) defines the clock enables used to control clocks to a set of peripherals. Unused peripherals

can have their clock stopped, reducing power consumption. In addition, the SPCR contains a read-only bit for the system PLL lock

status. At reset, the clock enables are set, enabling all system PLL gated output clocks.

Table iv. MCF548x Revision History (continued)

Section/Page

Substantive Changes

Table 2. System PLL Memory Map

MBAR Offset

Name

Byte0

Byte1

Byte2

Byte3

Access

0x300

System PLL Control Register

SPCR

R/W

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R PLLK

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

COR

EN

CRY

ENB

CRY

ENA

CAN1

EN

0

PSC

EN

0

USB

EN

FEC1

EN

FEC0

EN

DMA

EN

CAN0

EN

FB

EN

PCI

EN

MEM

EN

W

Reset

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Addr

MBAR + 0x300

Figure 2. System PLL Control Register (SPCR)

Table 3. SPCR Field Descriptions

Bits

Name Description

31

PLLK

System PLL Lock Status - Read-only lock status of the system PLL.

1 PLL has obtained frequency lock

0 PLL has not locked

30-15

—

Reserved, should be cleared.

14

COREN

Core & Communications Sub-System Clock Enable - Controls clocks for the CF4 Core, System SRAM, CommBus

Arbiter, I2C, Comm Timers, and External DMA modules

13

CRYENB

Crypto Clock Enable B - Controls the fast clock to the SEC

12

CRYENA

Crypto Clock Enable A - Controls the slow clock to the SEC

11

CAN1EN

CAN1 Clock Enable

10

—

Reserved, should be cleared.

9

PSCEN

PSC Clock Enable - Controls clock for all PSC modules.

8

—

Reserved, should be cleared.

7

USBEN

USB Clock Enable

6

FEC1EN

FEC1 Clock Enable

5

FEC0EN

FEC0 Clock Enable

4

DMAEN

Multi-channel DMA Clock Enable

3

CAN0EN

CAN0 Clock Enable

2

FBEN

FlexBus Clock Enable

1

PCIEN

PCI Bus Clock Enable

0

MEMEN

Memory Clock Enable - Controls clocks of the SDRAM controller module