3 slt timer count register (scntn), Slt timer count register (scntn) -3, 3 slt timer count register (scnt n ) – Freescale Semiconductor MCF5480 User Manual

Page 351

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

12-3

12.2.3

SLT Timer Count Register (SCNTn)

Table 12-3. SCRn Field Descriptions

Bits

Name Description

31–27

—

Reserved, should be cleared.

26

RUN

Run or wait mode

0 Timer counter expires, but then waits until the timer is cleared (either by writing 1 to the status

bit or by disabling and re-enabling the timer), before resuming operation.

1 Timer is enabled, and runs continuously. When the timer counter expires the terminal count

value immediately is reloaded and resumes counting down.

25

IEN

Interrupt enable. A CPU interrupt is generated only if this bit is set.

0 Interrupt is not generated

1 Interrupt is generated

This bit does not affect operation of the timer counter or status bit registers.

24

TEN

Timer enable

0 Timer is reset, then remains idle

1 Normal timer operation

23–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

CNT

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

CNT

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x908 (SCNT0), + 0x918 (SCNT1)

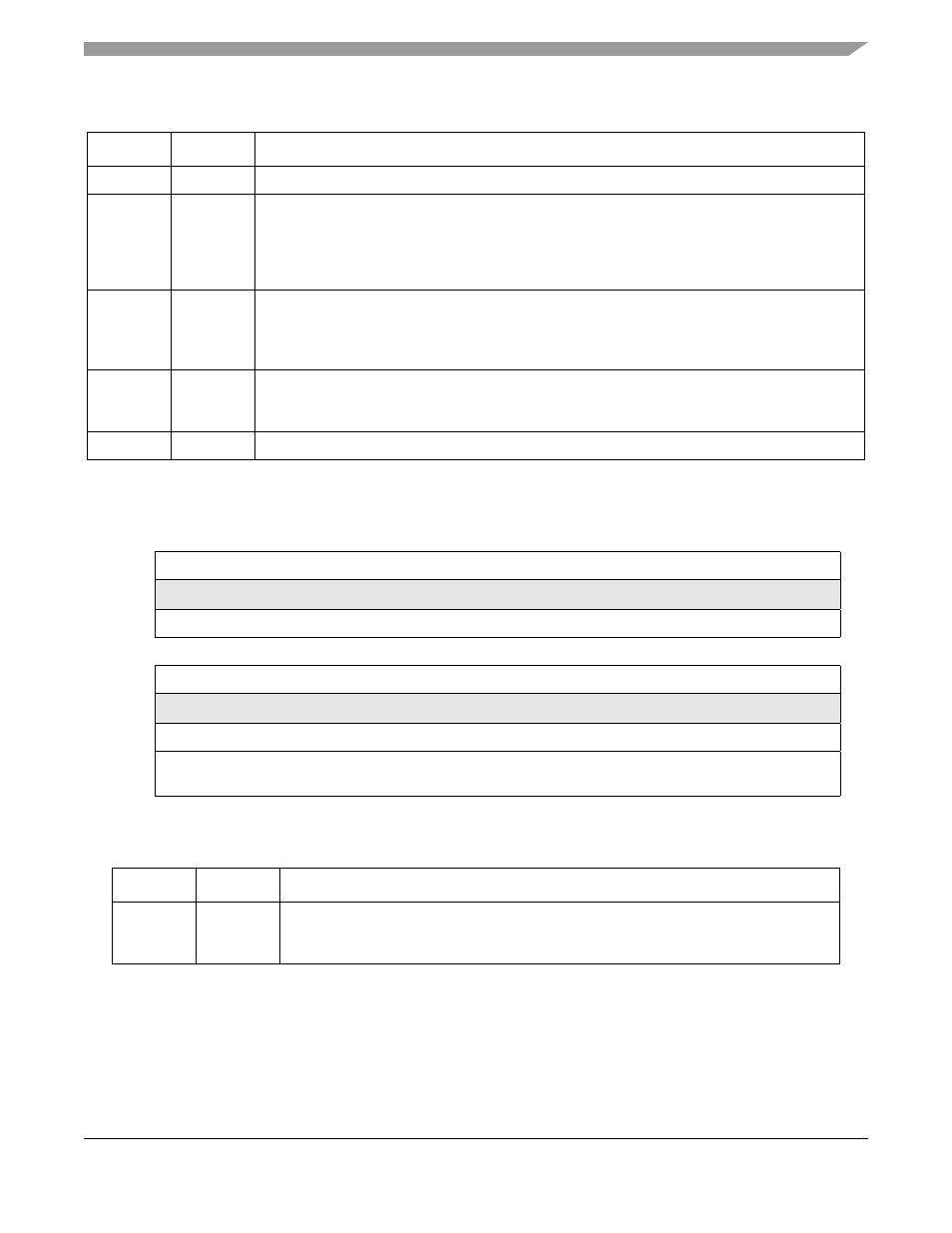

Figure 12-3. SLT Count Register (SCNTn)

Table 12-4. SCNTn Field Descriptions

Bits

Name Description

31–0

CNT

Timer count. GPIO output bit set. Provides the current state of the timer counter. This

register does not change while a read is in progress, but the actual timer counter continues

unaffected.