2 byte lanes, 3 address latch, Byte lanes -2 – Freescale Semiconductor MCF5480 User Manual

Page 418: Address latch -2

MCF548x Reference Manual, Rev. 3

17-2

Freescale Semiconductor

17.2

Byte Lanes

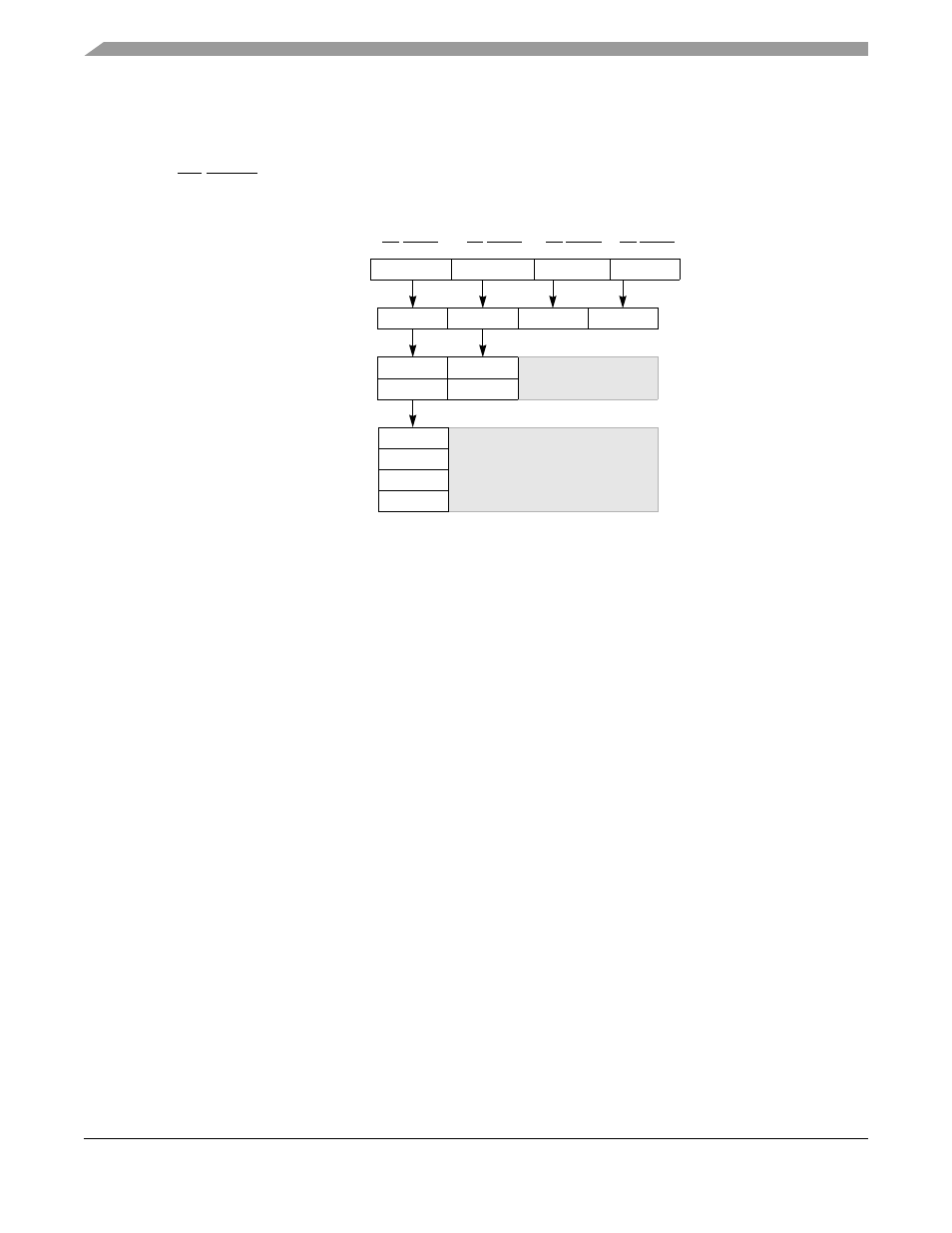

shows the byte lanes that external memory should be connected to and the sequential transfers

if a longword is transferred for three port sizes. For example, an 8-bit memory should be connected to

AD[31:24] (BE/BWE0). A longword transfer takes four transfers on AD[31:24], starting with the MSB

and going to the LSB.

Figure 17-1. Connections for External Memory Port Sizes

17.3

Address Latch

Because the FlexBus uses a multiplexed address and data bus, external logic might be needed in some

cases to capture the address phase as shown in

.

Processor

Data Bus

Byte 0

8-Bit Port

16-Bit Port

32-Bit Port

Byte 1

Byte 2

Byte 3

Byte 0

Byte 1

Byte 2

Byte 3

Byte 0

Byte 1

Byte 2

Byte 3

AD[31:24]

AD[23:16]

AD[15:8]

AD[7:0]

External

Memory

Memory

Memory

Byte Select

Driven with

address values

Driven with

address values

BE/BWE0

BE/BWE1

BE/BWE2

BE/BWE3