1 ethernet interrupt event register (eir), Ethernet interrupt event register (eir) -10 – Freescale Semiconductor MCF5480 User Manual

Page 940

MCF548x Reference Manual, Rev. 3

30-10

Freescale Semiconductor

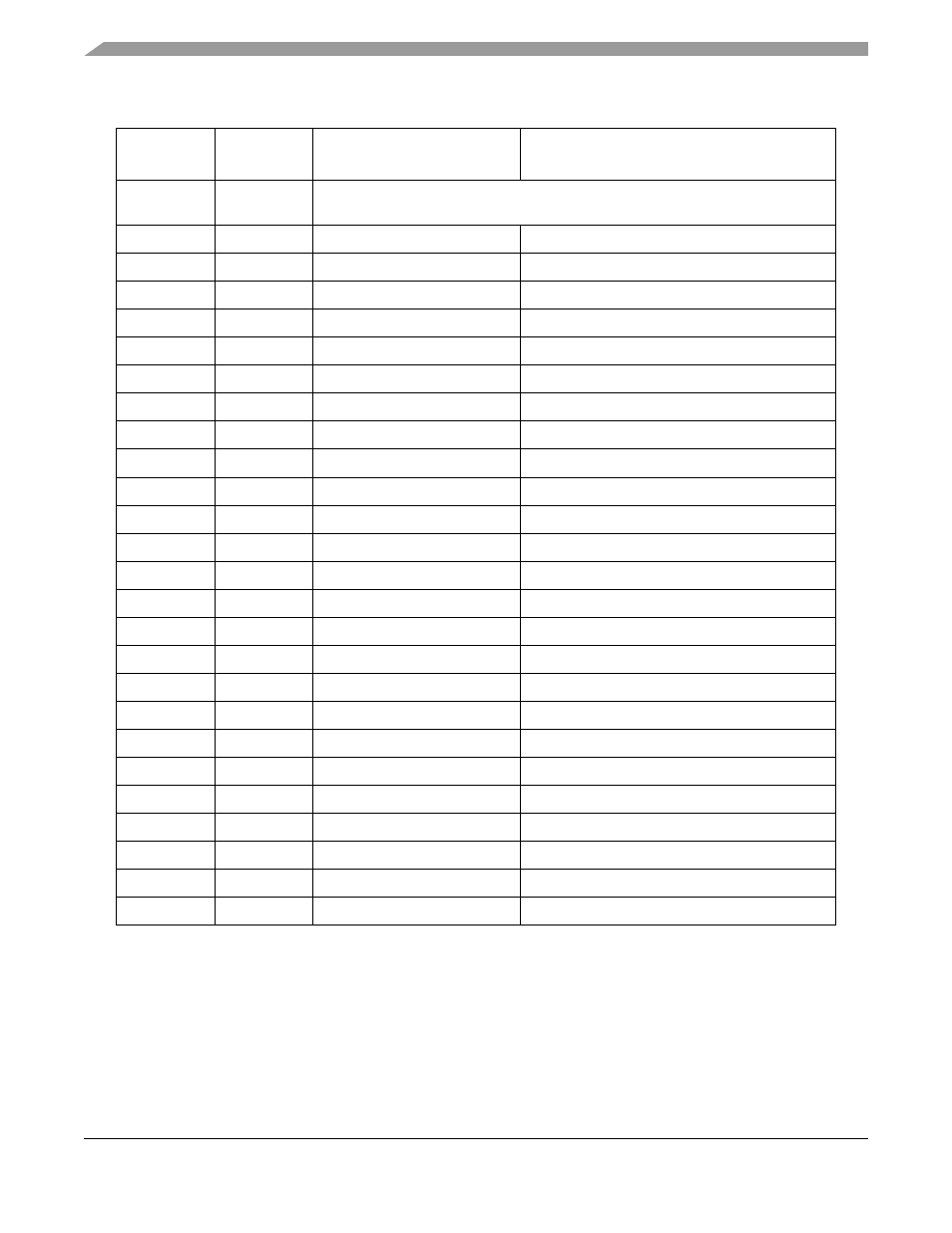

30.3.3.1

Ethernet Interrupt Event Register (EIR)

When an event occurs that sets a bit in the EIR, an interrupt will be generated if the corresponding bit in

the interrupt mask register (EIMR) is also set. The bit in the EIR is cleared if a one is written to that bit

position; writing zero has no effect. This register is cleared upon hardware reset.

These interrupts can be divided into operational interrupts, transceiver/network error interrupts, and

internal error interrupts. Interrupts which may occur in normal operation are GRA, TXF, and MII.

0x9278–

0x927C

0x9A78–

0x9A7C

Reserved

0x9280

0x9A80

RMON_R_DROP

Count of frames not counted correctly

0x9284

0x9A84

RMON_R_PACKETS

RMON Rx packet count

0x9288

0x9A88

RMON_R_BC_PKT

RMON Rx Broadcast Packets

0x928C

0x9A8C

RMON_R_MC_PKT

RMON Rx Multicast Packets

0x9290

0x9A90

RMON_R_CRC_ALIGN

RMON Rx Packets w CRC/Align error

0x9294

0x9A94

RMON_R_UNDERSIZE

RMON Rx Packets < 64 bytes, good crc

0x9298

0x9A98

RMON_R_OVERSIZE

RMON Rx Packets > MAX_FL bytes, good crc

0x929C

0x9A9C

RMON_R_FRAG

RMON Rx Packets < 64 bytes, bad crc

0x92A0

0x9AA0

RMON_R_JAB

RMON Rx Packets > MAX_FL bytes, bad crc

0x92A4

0x9AA4

RMON_R_RESVD_0

0x92A8

0x9AA8

RMON_R_P64

RMON Rx 64 byte packets

0x92AC

0x9AAC

RMON_R_P65TO127

RMON Rx 65 to 127 byte packets

0x92B0

0x9AB0

RMON_R_P128TO255

RMON Rx 128 to 255 byte packets

0x92B4

0x9AB4

RMON_R_P256TO511

RMON Rx 256 to 511 byte packets

0x92B8

0x9AB8

RMON_R_P512TO1023

RMON Rx 512 to 1023 byte packets

0x92BC

0x9ABC

RMON_R_P1024TO2047

RMON Rx 1024 to 2047 byte packets

0x92C0

0x9AC0

RMON_R_P_GTE2048

RMON Rx packets w > 2048 bytes

0x92C4

0x9AC4

RMON_R_OCTETS

RMON Rx Octets

0x92C8

0x9AC8

IEEE_R_DROP

Count of frames not counted correctly

0x92CC

0x9ACC

IEEE_R_FRAME_OK

Frames Received OK

0x92D0

0x9AD0

IEEE_R_CRC

Frames Received with CRC Error

0x92D4

0x9AD4

IEEE_R_ALIGN

Frames Received with Alignment Error

0x92D8

0x9AD8

IEEE_R_MACERR

Receive Fifo Overflow count

0x92DC

0x9ADC

IEEE_R_FDXFC

Flow Control Pause frames received

0x92E0

0x9AE0

IEEE_R_OCTETS_OK

Octet count for Frames Rcvd w/o Error

Table 30-6. MIB Counters Memory Map (Continued)

MBAR Offset

for FEC0

MBAR Offset

for FEC1

Mnemonic

Description