Usb endpoint – Freescale Semiconductor MCF5480 User Manual

Page 909

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

29-35

29.2.5.2

USB Endpoint n Interrupt Status Register (EPnISR)

The EPnISR monitors the status of a specific endpoint and generates a CPU interrupt each time a

monitored event occurs.

An interrupt, once set, remains set until cleared by writing a 1 to the corresponding bit. Interrupts do not

clear automatically if the event that caused them goes away (for example, if an endpoint FIFO is emptied

and then filled with no intervention from software, both EMT and FU would be set). Writing a 0 has no

effect.

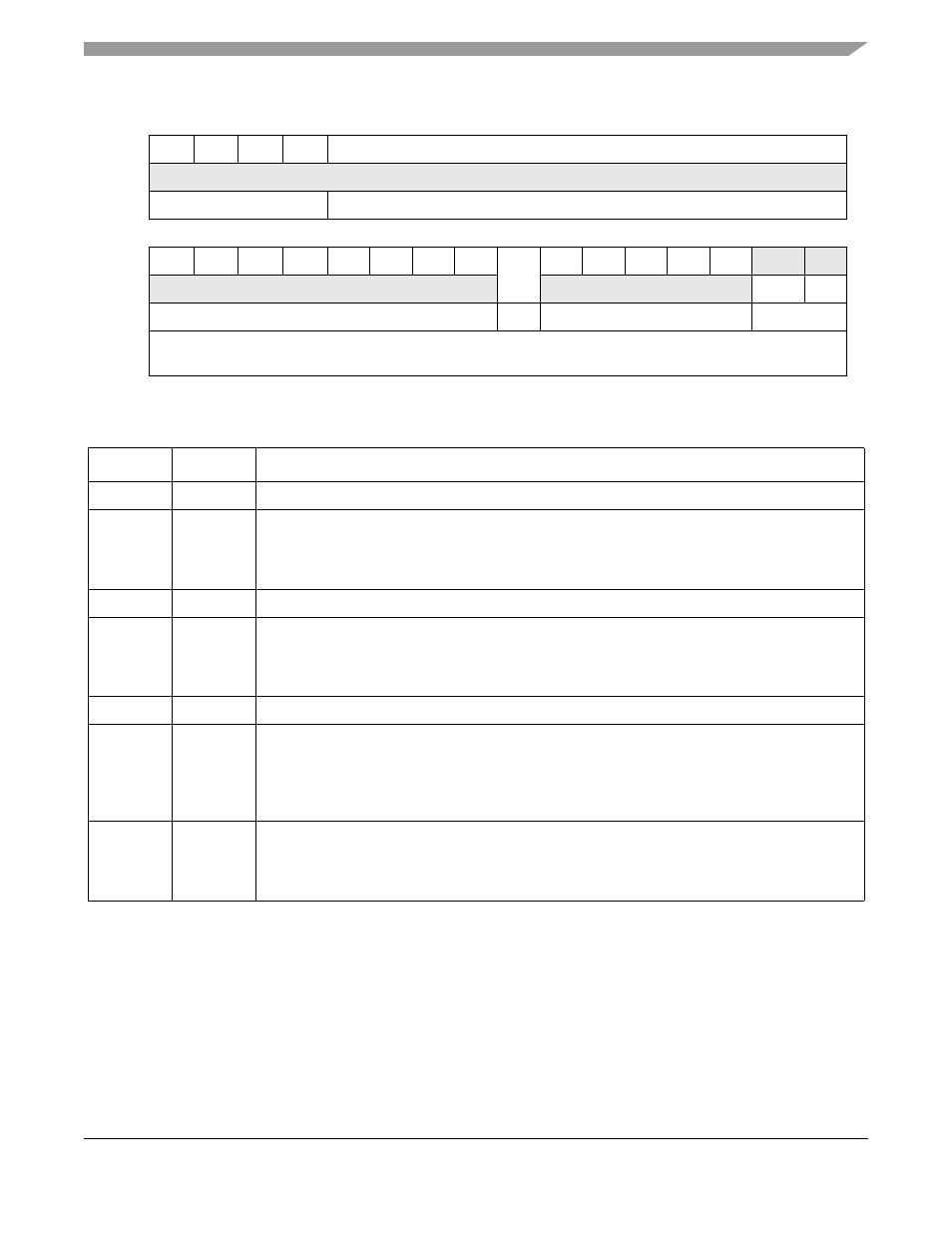

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

BYTECNT

W

Reset

Uninitialized

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

DIR

0

0

0

0

0

W

FLUSH RST

Reset

Uninitialized

0

Uninitialized

0

0

Reg

Addr

MBAR + 0xB440 (EP0STAT); 0xB470 (EP1STAT); 0xB4A0 (EP2STAT); 0xB4D0 (EP3STAT);

0xB500 (EP4STAT); 0xB530 (EP5STAT); 0xB560 (EP6STAT)

Figure 29-41. USB Endpoint n Status and Control Register (EPnSTAT)

Table 29-36. EPnSTAT Field Descriptions

Bits

Name

Description

31–28

—

Reserved, should be cleared.

27–16

BYTECNT

Byte count. This field indicates the number of bytes currently stored in the associated FIFO. This

value is a "live" count that does not differentiate between data that is from accepted or

not-yet-accepted data packets. Thus, the value may jump around in cases where packets are

discarded or retransmitted.

15–8

—

Reserved, should be cleared.

7

DIR

Direction. This is the transfer direction. This bit also determines the direction of the endpoint FIFO.

This bit should be set appropriately before responding to transfer requests from the host.

0 OUT Endpoint (from host to device).

1 IN Endpoint (from device to host).

6–2

—

Reserved, should be cleared.

1

FLUSH

Flush. This write only bit causes the associated FIFO to be flushed to its empty state. All FIFO

pointers will be reset to the empty state while FIFO configuration registers (USB_EPn_FCR) retain

their values.

0 Do nothing.

1 Initiate flush operation.

0

RST

Reset. This write only bit causes the associated FIFO to be reset. All configuration data will be lost

and the FIFO pointers will reset to the empty state.

0 Do nothing.

1 Initiate reset operation.