Table 14. atu outbound data flow ordering rules, 14 atu outbound data flow ordering rules, Table 14, “atu outbound data flow – Intel CONTROLLERS 413808 User Manual

Page 88

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

88

Order Number: 317805-001US

Definitions of the terms used in

and

are as follows. PCI terms are

noted in parenthesis:

• Inbound Write (PMW) - Data from a write cycle initiated on PCI and targeted at the

internal bus. Note that the address is in a separate transaction queue and is not

referenced.

• Inbound Read Request (DRR-PCI mode and SRR-PCI-X mode) - address information

from a read transactions retried or split on the PCI bus. Mastered on the internal

bus to retrieve data for the Inbound Read Completion.

• Inbound Configuration Write Request - (DWR- PCI mode and SWR - PCI-X mode) -

The address and data associated with a configuration write transaction from PCI

and targeted at the ATU PCI configuration address space. Once completed on the

internal bus, creates an Inbound Configuration Write Completion.

• Outbound Read Completion (SRC) - The data read on PCI in the process of being

returned to the internal bus. This data is the completion cycle that results from an

Outbound Read Request.

• Outbound Write (PMW) - The address and data from a write initiated on the internal

bus and eventually completing on the PCI bus.

• Outbound Read Request (SRR) - The address/command of a split read cycle

initiated on the internal bus. The read data is returned in the Outbound Read

Completion cycle.

• Inbound Read Completion (DRC-PCI mode and SRC-PCI-X mode) - The data read

on the internal bus in the process of being returned to the PCI bus. This data is the

completion cycle for an Inbound Read Request.

• Inbound Configuration Write Completion (DWC-PCI mode and SWC-PCI-X mode) -

The status of an inbound write configuration cycle traveling from the internal bus

back towards the PCI bus.

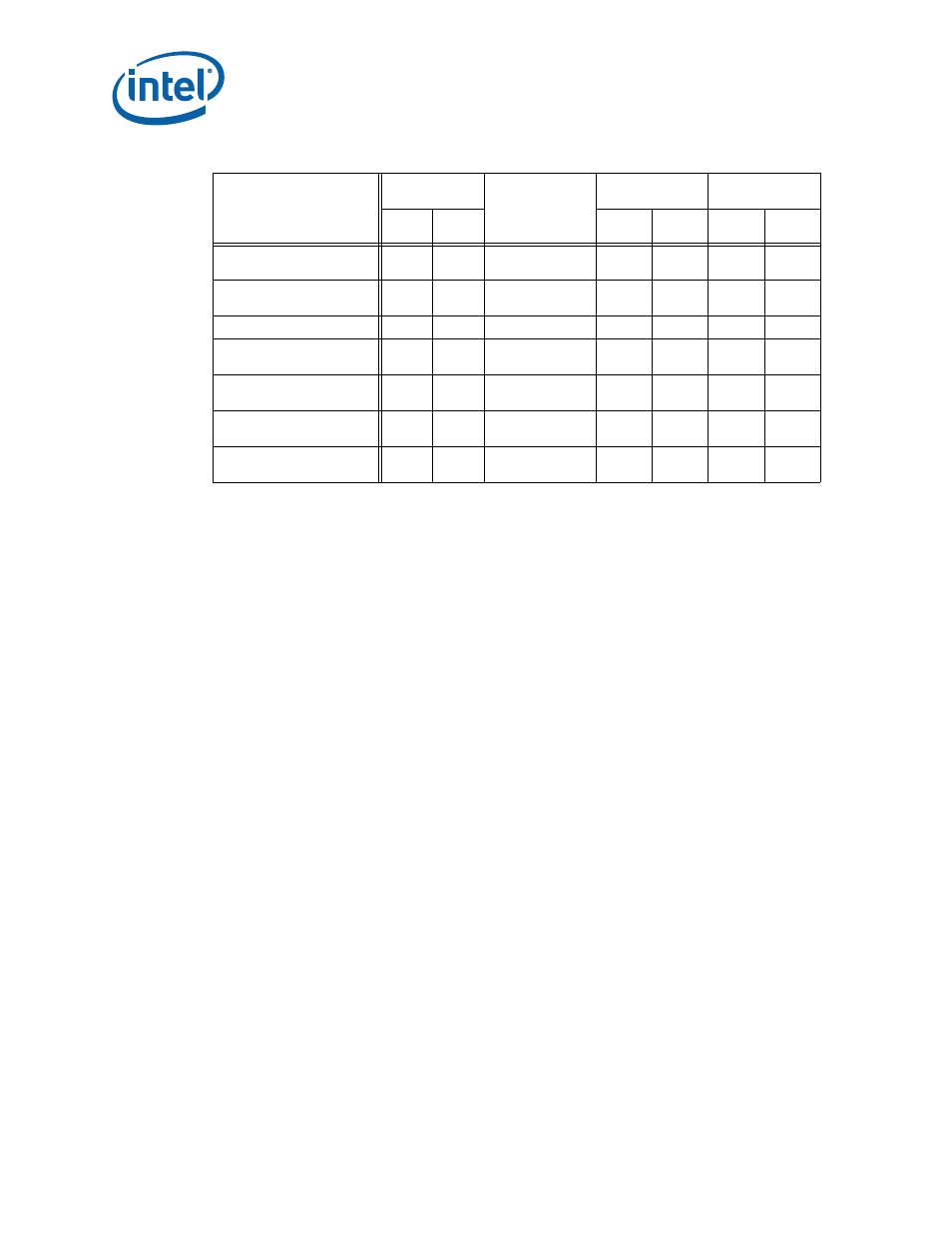

Table 14. ATU Outbound Data Flow Ordering Rules

Row Pass Column?

Outbound

Write

Outbound Read

Request

Inbound Read

Completion

Inbound Write

Completion

Posted Non-

Posted

DRC

SRC

DWC

a

SWC

b

Outbound Posted Write

Request

No

Yes

Yes

Yes

Yes

Yes

Yes

Outbound Non-posted

c

Write Request

No

No

No

Yes

Yes

Yes

Yes

Outbound Read Request

No

No

No

Yes

Yes

Yes

Yes

Inbound Delayed Read

Completion (DRC)

No

Yes

Yes

Yes

NA

Yes

NA

Inbound Split Read

Completion (SRC)

No

Yes

Yes

NA

Yes

NA

No

Inbound Delayed Write

Completion (DWC)

No

Yes

Yes

Yes

NA

NA

NA

Inbound Split Write

Completion (SWC)

No

Yes

Yes

NA

Yes

NA

NA

a. Since the Inbound DWR transaction queue is one-deep, the passing rule associated with DWC vs. DWC is

moot (i.e., NA).

b. Since the Inbound SWR transaction queue is one-deep, the passing rule associated with SWC vs. SWC is

moot (i.e., NA).

c. Outbound Non-posted writes include I/O writes and Configuration writes.