7 uart x modem control register, 454 uart x modem control register - (uxmcr), Section 13.4.7, uart x – Intel CONTROLLERS 413808 User Manual

Page 678: Modem control register, Section 13.4.7, uart x modem, Control register, Intel, Bit default description

Intel

®

413808 and 413812—UARTs

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

678

Order Number: 317805-001US

13.4.7

UART x Modem Control Register

This register controls the interface with the modem or data set (or a peripheral device

emulating a modem). The contents of the Modem Control register are described below:

Table 454. UART x Modem Control Register - (UxMCR) (Sheet 1 of 2)

Bit

Default

Description

31:6

000 0000h

Reserved

5

0

2

Autoflow Control Enable (AFE): When set, autoflow control is enabled. Only

auto-CTS is enabled when RTS is cleared in MCR while AFE is set. Both auto-CTS

and auto-RTS are enabled when AFE and RTS in MCR are set. Auto-RTS is not

enabled when AFE is not set regardless of the state of RTS.

Autoflow automates the flow of data between the UART and the remote device. See

Section 13.3.4, “Autoflow Control” on page 665

for more details.

0 = Auto-RTS and Auto-CTS are disabled

1 = Auto-CTS is enabled. IF RTS in MCR is also set, both auto-CTS and auto-RTS

is enabled

4

0

2

Loop back test mode (LOOP): This bit provides a local Loopback feature for

diagnostic testing of the UART.

In the Diagnostic mode, data that is transmitted is

immediately received. This feature allows the processor to verify the UART Transmit

and Receive data paths. The Transmit, Receive and Modem Control Interrupts are

operational. The modem-control input CTS# is activated by MCR bit 1 instead of the

modem-control input. A Break signal can also be transferred from the transmitter

section to the receiver section in Loop-Back mode.

When LOOP is set (1), the following occurs:

•

The TXD (transmitter output) pin is set to a logic-1 state.

•

The RXD (receiver input) pin is disconnected.

•

The output of the Transmitter Shift register is “looped back” into the

Receiver-Shift register input.

•

The modem-control input CTS# is disconnected from the pins and the

modem-control output pin RTS# is forced to the inactive state.

The RTS bit of the Modem Control register is connected to bits of the Modem Status

register bits. Flow control can be tested; when autoflow is enabled the RTS bit of the

Modem Control Register has no effect on the CTS# input as RTS# is asserted by the

autoflow logic.:

•

RTS = 1 forces CTS to a 1

Note:

Note: Coming out of the Loop-Back Test mode may result in unpredictable

activation of the delta bit (bit 0) in the Modem Status register (MSR). It is

recommended that MSR is read once to clear the delta bits in the MSR.

0 = Normal UART operation

1 = Test mode UART operation

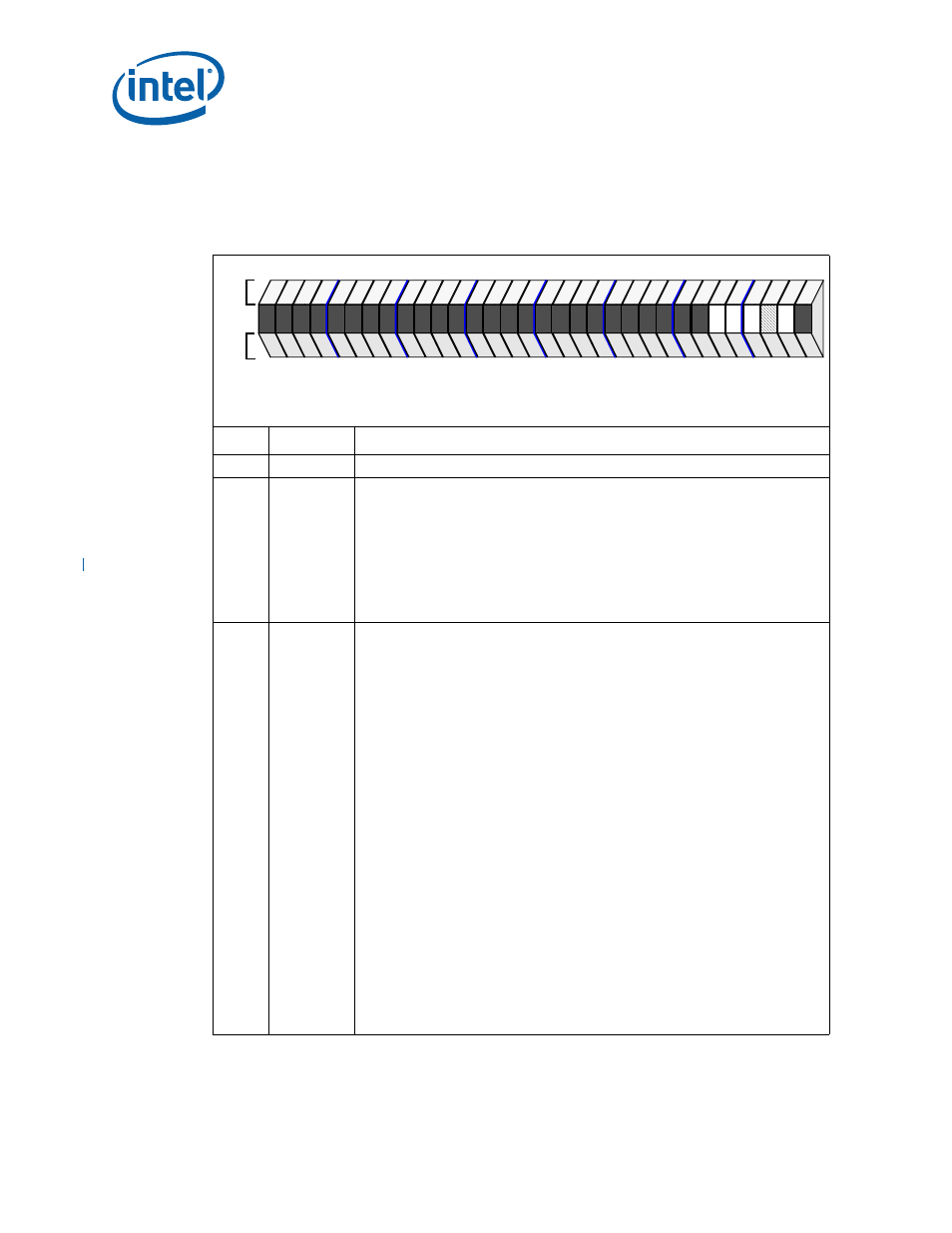

PC

I

IO

P

A

tt

ri

bu

te

s

A

tt

ri

bu

te

s

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

pr

na

rw

na

rv

na

Unit #

01

Intel XScale

®

Core internal bus address

+2310H (DLAB=x)

+2350H (DLAB=x)

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible