11 multi-function support, 1 pci-x interface control parameters, Table 20. pci-x interface control parameters usage – Intel CONTROLLERS 413808 User Manual

Page 130: 20 pci-x interface control parameters usage, Multiple functions are not supported for 4138xx

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

130

Order Number: 317805-001US

2.11

Multi-Function Support

Multiple functions are not supported for 4138xx.

2.11.1

PCI-X Interface Control Parameters

The following registers are located in the configuration space header and extended

space and provide control of the PCI Interface. The effect of each bit is detailed below.

Note:

is referring to only enabled functions. In root complex mode multi-function is

not applicable.

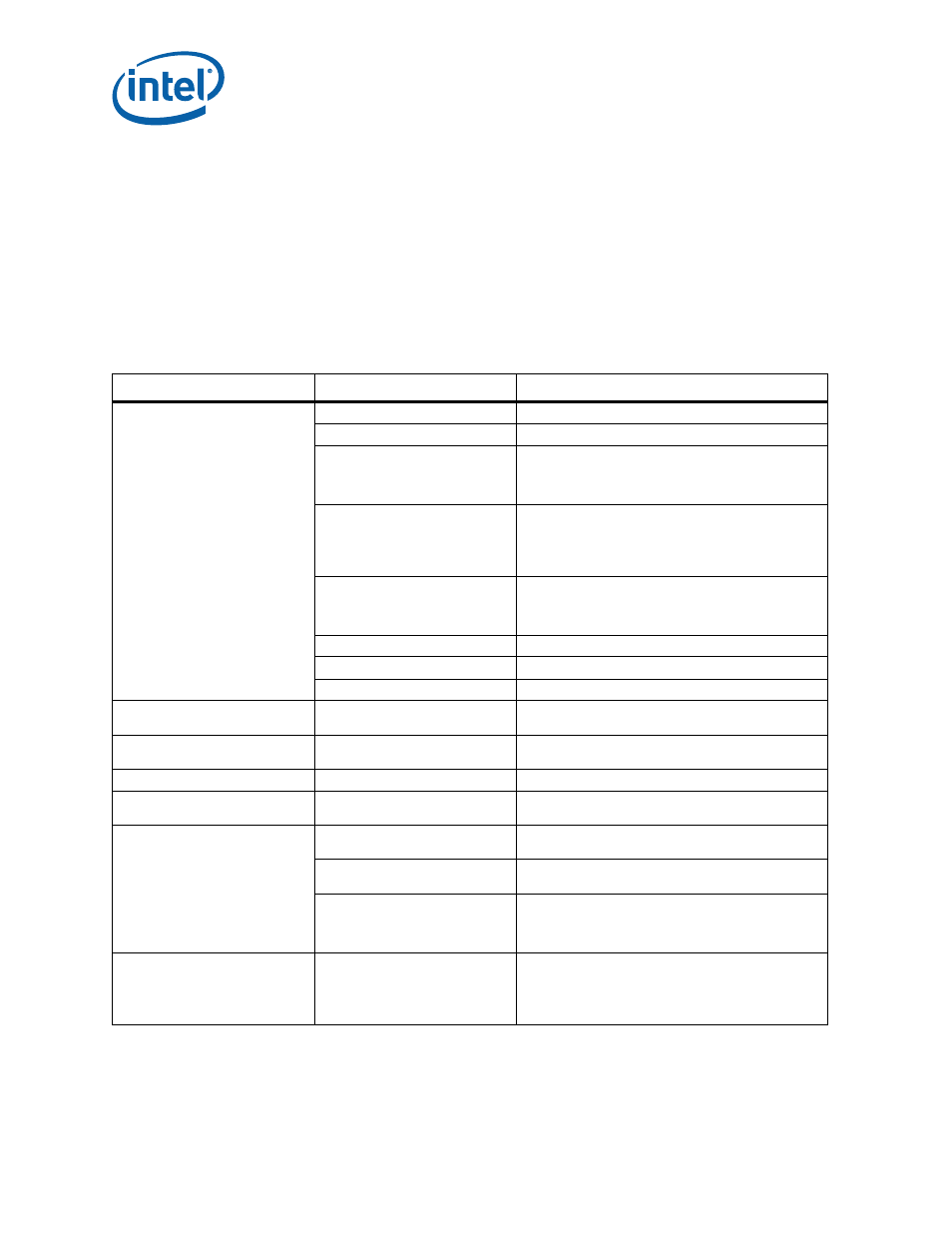

Table 20. PCI-X Interface Control Parameters Usage

Register Name

Register Bits Description

Usage

Bit 10 - Interrupt Disable

Each function can independently control this bit.

Bit 9 - Fast Back-to-Back Enable

Not applicable, since this is not supported.

Bit 8 - SERR# Enable

SERR# bit from each function is logically ORed and

then fed to the PCI Interface. This implies that SERR#

is globally enabled when only one of the functions

enables SERR#.

Bit 6 - Parity Error Response

Parity Error Response bit from each function is

logically ORed and fed to the PCI Interface. This

implies that Parity Error Response is globally enabled

when only one of the functions enables Parity Error

Response.

Bit 4 - MWI Enable

MWI Enable bit from each function is logically ORed

and then fed to the PCI Interface. This implies that

MWI Enable is globally enabled when only one of the

functions enables MWI Enable.

Bit 2 - Bus Master Enable

Each function can independently control this bit.

Bit 1 - Memory Enable

Each function can independently control this bit.

Bit 0 - I/O Enable

Each function can independently control this bit.

Entire Register

Provided by function 0. For 4138xx, the ATU provides

this parameter.

Entire Register

Each function can independently control this register.

Entire Register

Each Function can independently control this register

Entire Register

Each Function can independently control this register

Bit[6:4] - Maximum Outstanding

Split Transactions

The PCI Interface sums the values from each function

and use the result as the parameter.

Bit[3:2] - Maximum Memory Read

Byte Count

The PCI Interface uses the least common denominator

(LCD) based on the values from all the functions.

Bit0 - Uncorrectable Error

Recovery

Uncorrectable Error Recovery bit from each function is

logically ANDed and then fed to the PCI Interface. This

implies that Uncorrectable Error Recovery is enabled

when all of the functions enable this capability.

Bit 30 - Disable Single-Bit Error

Correction

Disable Single-Bit Error Correction bit from each

function is logically ANDed and then fed to the PCI

Interface. This implies that Disable Single-Bit Error

Correction is disabled when all of the functions disable

this capability.