14 mu upper base address register - muubar, Table 279. mu upper base address register - muubar, 279 mu upper base address register - muubar – Intel CONTROLLERS 413808 User Manual

Page 424: Mu upper base address register - muubar, Section 4.7.14, “mu upper, Base address register - muubar

Intel

®

413808 and 413812—Messaging Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

424

Order Number: 317805-001US

4.7.14

MU Upper Base Address Register - MUUBAR

The MU Upper Base Address Register (MUUBAR) contains the upper 4-bit of the 36-bit

local memory base address of the MU address space as depicted in

. For

example, the MU address space as viewed from Host I/O Interface interface. The MU

base address is required to be located on a 8-KByte boundary. The lower 32-bits of the

MU Base Address are located in the MU Upper Address Register (MUBAR). Refer to

Section 4.7.13, “MU Base Address Register - MUBAR” on page 423

.

Note:

The default values of MUBAR/MUBAR are programmed to match the default values

programmed in the Inbound ATU Translate Value Register 0 - IATVR0/Inbound ATU

Upper Translate Value Register 0 - IAUTVR0. This allows the MU registers to be mapped

in the first 8-KByte of the PCI Window 0 Address space.

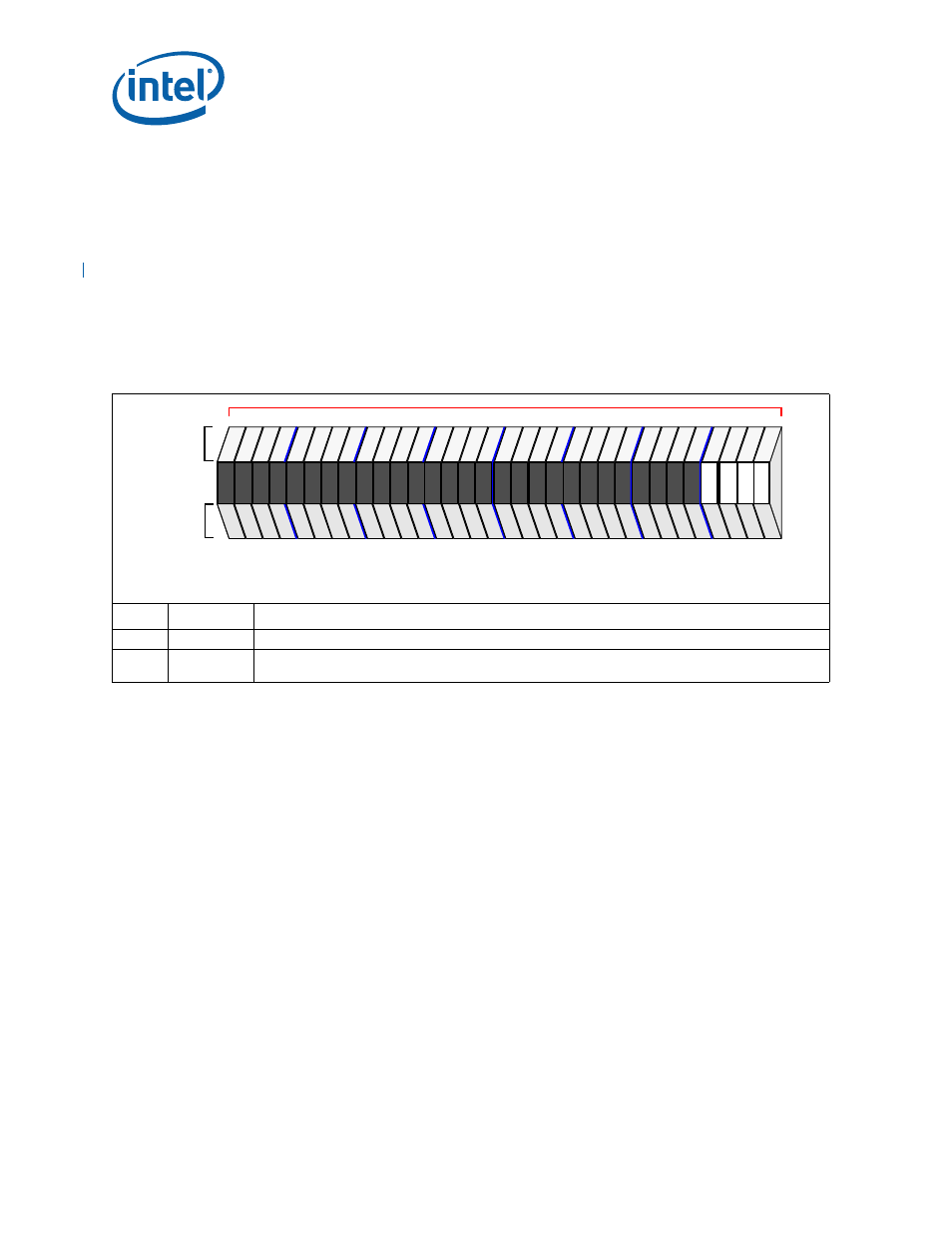

Table 279. MU Upper Base Address Register - MUUBAR

Bit

Default

Description

31:04

0000000H Reserved

03:00

0H

MU Upper Base Address - Local memory address of the MU (including MSI-X) registers as viewed from

Host I/O Interface. The MU occupies a 8-KByte space from Host I/O Interface.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rv rw rw rw rw

na

na na na na na na na na na na na na na na na

na na na

na na na na na na na na na na na na

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

MUUBAR

internal bus address offset

4088H