2 address translation unit (pci-e), 545 intel, Table 545. intel – Intel CONTROLLERS 413808 User Manual

Page 814

Intel

®

413808 and 413812—Peripheral Registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

814

Order Number: 317805-001US

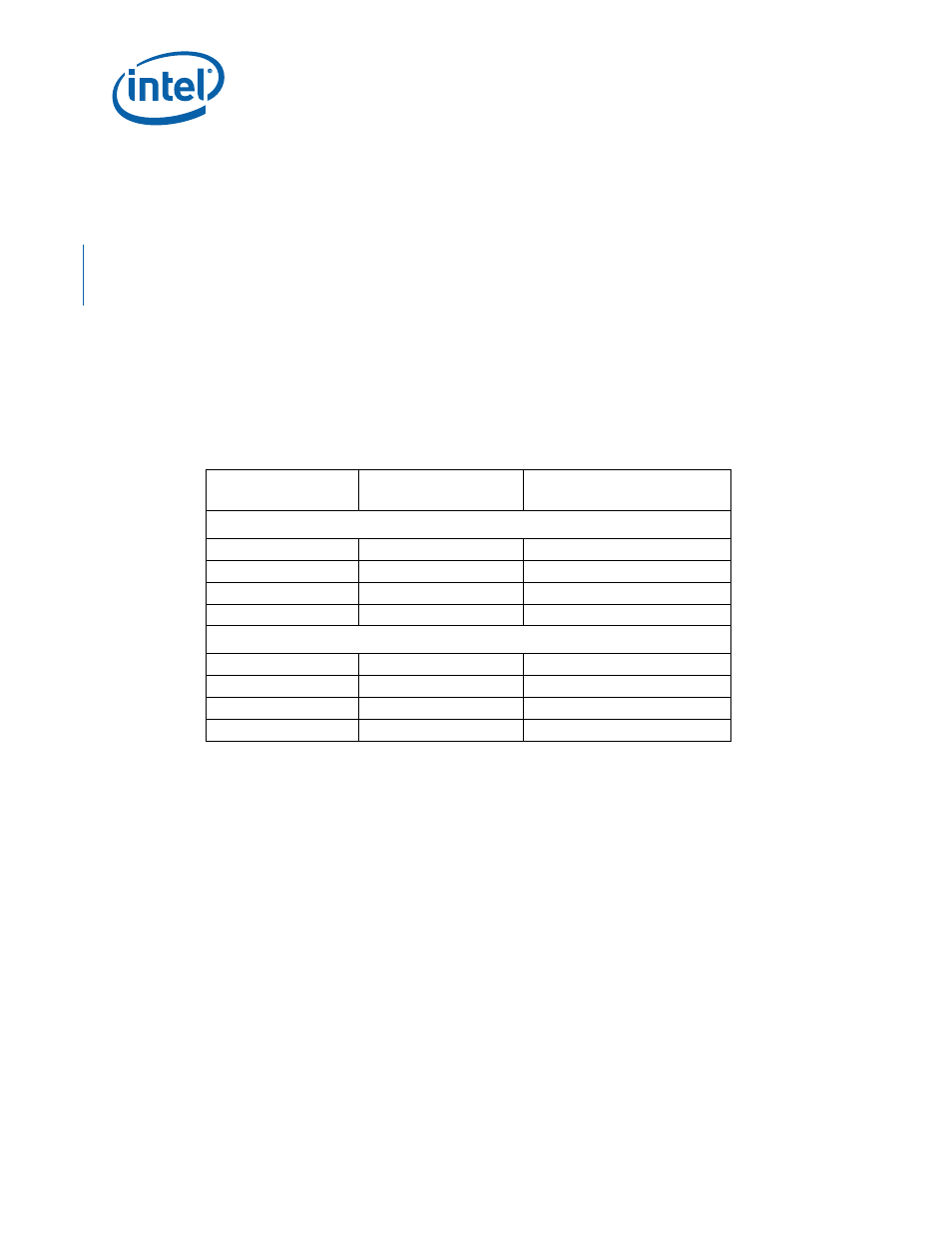

19.6.2.2 Address Translation Unit (PCI-E)

All of the ATU registers are accessible through both inbound PCI configuration cycles

and the 4138xx core CPU (Register offsets 000H through FFFH).

The Internal Bus Address Offset to PMMRBAR of any ATU Register can be derived by

adding the 4 KB address aligned ATUE Base Address Offset (

and 413812 I/O Controllers ATUE Configuration Space Base Address Offset” on

Table 546, “Address Translation Unit Registers —

For example, when INTERFACE_SEL_PCIX# and CONTROLLER_ONLY# are both

asserted, the offset to PMMRBAR of the ATU Command Register would be

(4 D000H+004H) or 4 D004H.

Note:

The 4 KB Address Aligned Range Offset can be different depending on two configuration

.

Table 545. Intel

®

413808 and 413812 I/O Controllers ATUE Configuration Space Base

Address Offset

CONTROLLER_ONLY# INTERFACE_SEL_PCIX#

ATUE Base Address Offset

(Relative to PMMRBAR)

PCI Attributes

Deasserted

Deasserted

+4 0000H

Asserted

Deasserted

+4 5000H

Asserted

Asserted

+4 5000H

Deasserted

Asserted

+4 5000H

Local Attributes

Deasserted

Deasserted

+4 8000H

Asserted

Deasserted

+4 D000H

Asserted

Asserted

+4 D000H

Deasserted

Asserted

+4 D000H